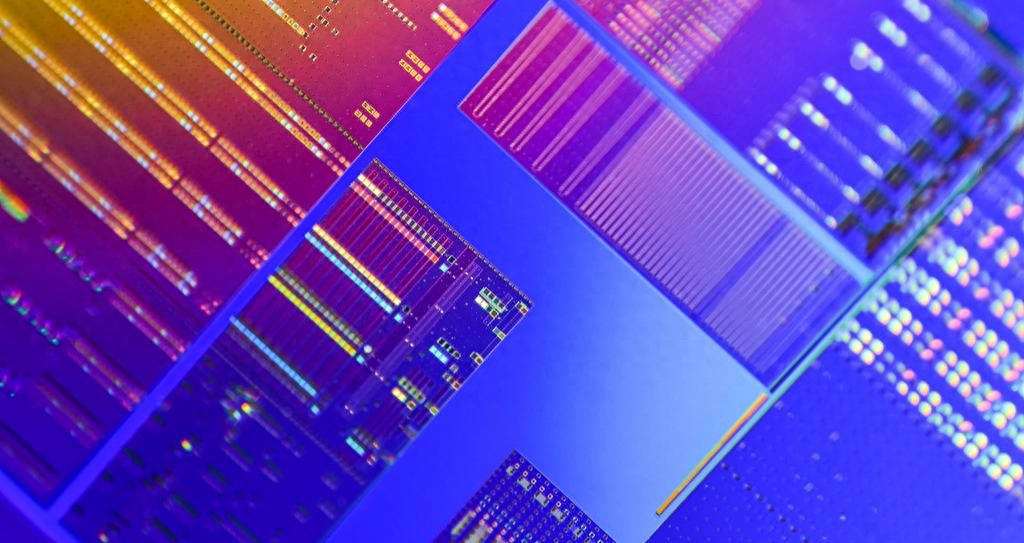

據報道 , 三星電子正在研發的下一代定制化HBM4E基底芯片已進入后端設計階段 , 標志著該產品的研發工作跨過了中期節點 。

基底芯片是HBM最底層的控制區域 , 負責完成堆疊式DRAM的數據讀寫、錯誤修正等核心操作 , 直接決定HBM的性能與穩定性 。 近期 , 客戶企業提出了定制化HBM的需求 , 要求在基底芯片中集成多種邏輯功能 。 后端設計是指在寄存器傳輸級(RTL)邏輯電路設計等前端開發完成后 , 對實際電路進行布局與連接的物理設計階段 。 后端設計完成后 , 廠商會將最終的設計數據交付給晶圓代工企業 , 這一環節被稱為 “流片” 。

半導體行業相關人士表示:“三星電子近期在內部制定了全新的HBM產品路線圖 , 并且已經緊急要求合作企業在今年3月前 , 按照該路線圖制定所需產品的供需計劃 。 ”這份路線圖涵蓋了計劃于今年量產的第六代HBM4、第七代HBM4E以及第八代HBM5等產品 。

【三星電子HBM4E基底芯片,進入后端設計階段】分析認為 , 三星此次制定新路線圖 , 意在將這些下一代HBM的量產時間提前 , 并強化定制化HBM的發展戰略 。

去年 12 月 , 相關人士在一場研討會上透露:“三星電子從 HBM4 產品開始 , 同步推進標準HBM和定制化HBM兩條產品線 , 近期還分別為谷歌、Meta 以及英偉達的定制化HBM項目擴充設計人員 , 新增人員規模達 250 人 。 ” 行業預計 , HBM4E將于2027年推出 , HBM5則計劃在2029年面世 。

一位熟悉三星電子的業內人士預測:“HBM4 仍以通用型產品為主 , 而從HBM4E和HBM5開始 , 三星將轉向定制化HBM的生產 。 屆時 , 如何與晶圓代工企業合作完成基底芯片的邏輯設計 , 將成為關鍵所在 。 ”

目前 , 三星電子正處于定制化HBM4E基底芯片的物理實現階段 , 同時對EDA工具環境進行優化 , 這些工作均屬于后端設計范疇 。 內存接口電路設計專家任大賢(音譯)碩士牽頭負責物理實現的核心環節 —— 輸入輸出(I/O)設計 。 該碩士曾任職于 IBM 和格芯等企業 , 并于 2023 年加入三星電子 。

定制化HBM4E基底芯片的設計工作 , 由曾主導HBM4研發的核心人員負責 。 該研發團隊在完成 HBM4 的開發工作后 , 已于去年 11 月并入 DRAM 研發部門 。 據悉 , 三星電子正依托這支團隊 , 同步推進定制化HBM5基底芯片的設計籌備工作 。

通常情況下 , 一款HBM的整體設計周期約為 10 個月 , 其中后端設計階段占比高達 60% 至 70% 。 一家無晶圓廠企業的相關人士解釋道:“在后端設計過程中 , 需要與前端設計環節進行交互修正與驗證 , 前端和后端的耗時占比大致為 4:6 。 ” 業內預計 , 定制化HBM4E的設計工作將于今年 5 月至 6 月完成 。

據悉 , SK 海力士和美光科技也有望在相近時間點完成各自定制化HBM4E的研發工作 。 一位內存行業相關人士表示:“目前三大內存廠商的HBM4E研發進度基本持平 , 尚未出現明顯的領先或落后情況 。 ”

與此同時 , 三星電子DS部門內存業務部正在參與JEDEC的HBM5標準化工作 , 由該業務部的夏慶洙(音譯)常務牽頭推進 , 同步開展HBM5產品的規劃工作 。

另一位業內人士表示:“企業通常會在參與 JEDEC 標準制定的同時 , 推進相關產品的研發 , SK 海力士同樣在參與HBM5標準化工作的過程中 , 開展對應的產品研發 。 ” 他補充道:“從 HBM4 開始 , 廠商已根據客戶需求 , 在基底芯片中集成部分GPU運算能力、散熱控制以及錯誤控制功能 。 預計 SK 海力士也將從HBM4E起 , 明確區分通用型HBM與定制化HBM兩條產品線 , 分別進行研發準備 。 ”

想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 三星 Galaxy Z TriFold 評測:三折疊的新路線,生產力的再飛躍

- 三星和SK海力士削減NAND晶圓產量以提升利潤率

- 美國投資銀行稱三星2nm良率或不足40%,未來將被英特爾反超

- 蘋果三星做不好的“Air”,國產廠商怎么就搞成了

- TechWeb微晚報:Siri轉型全能聊天機器人,“電子木魚”盲盒引爆熱搜

- 三星HBM4E Base Die已完成前段設計,將采用2nm制程代工

- 消息稱三星內存全線漲價80% 官方回應

- 蘋果入局AI Pin,或對標OpenAI,能否打破「電子垃圾」魔咒?

- 防窺進入系統級時代?三星 S26 內建隱私屏曝光,旗艦體驗被改寫

- 三星Galaxy S26系列發布時間曝光:延遲約一個月 最早2月25日發