文章圖片

文章圖片

文章圖片

文章圖片

本文由半導體產業縱橫(ID:ICVIEWS)編譯自Semiconductor Engineering

為保障良率 , I/O 測試和備用 lane 替換修復將更普遍 。

如今 , 高性能計算設備中集成了數萬個互連 , 為實現足夠的良率 , Chiplet 接口的冗余設計已成為必要 。 隨著這些互連數量和密度的增加 , 良率前景只會愈發黯淡 。

二十多年來 , 高速 I/O 接口一直包含管理現場系統板故障的可靠性策略 。 例如 , 2007 年推出的 PCI Express 2.0 標準包含 16 條事務 lane 。 但如果某條 lane 發生故障 , 只會使用其中 8 條 , 將使事務處理速率減半 。 這種通常被稱為 “優雅降級” 的策略 , 至今仍是 UCIe 等計算 Chiplet 接口所采用的策略 。

但如今 , HBM 和 UCIe 接口包含了多芯片組件中單 lane 故障的應急措施 , 規定了備用 lane 以替換 Chiplet 之間出現故障的信號互連 。 一旦檢測到故障 lane , 就會用備用 lane 進行替換 , 從而 “修復” 故障 lane 。 工程團隊可以在整個測試制造流程中更換有問題的 lane 。 這種能力還可用于客戶系統 , 以應對與組裝相關的可靠性和磨損故障機制 。

盡管如此 , 隨著先進的組裝工藝促成了高密度的 2.5D 和 3D 架構 , 基于 Chiplet 的系統中的信號互連數量將攀升至數十萬 , 將對制造和系統級可靠性的 I/O 測試及修復策略構成挑戰 。 因此 , 測試內容需要全面檢測與 I/O 相關的故障 。

“對于高容量、高數據速率的互連 lane , 設計人員需要考慮可能因交叉耦合和其他缺陷類型而顯現的各種故障 , ” 新思科技(Synopsys)多芯片測試相關 SLM 產品的首席產品經理費薩爾?戈里亞瓦拉(Faisal Goriawalla)表示 , “基于一套全面的算法測試圖形 , 如果發現任何 lane 存在缺陷 , 就必須有一套機制通過用良好的 lane 替換有問題的 lane 來進行 lane 修復 。 ”

其優勢在于 , 追蹤故障發生的位置和時間有助于工程團隊了解良率情況 。 Chiplet 信號路徑缺陷可能會影響 PHY(即 I/O 電路)、從 Chiplet 到中介層再到封裝襯底的冶金連接 , 以及相應的互連 。 由于需要驅動的傳輸線較短 , I/O 電路的設計布局在設計規則方面更為寬松 , 這反過來降低了 I/O 電路的故障率 。 同樣 , 重分布層(RDL)和中介層互連不會突破工藝極限 。

lane 修復主要是為了解決與硅通孔(TSV)、微凸點和混合焊盤相關的組裝工藝缺陷 。 歷史上 , 只有一兩個連接會受到缺陷的影響 。 然而 , 根據組裝技術的不同 , 主要的缺陷機制可能會發生變化 , 有缺陷的連接數量也會增加 。

“如果使用間距為 25 微米的 EMIB(英特爾的嵌入式多芯片中介層橋接技術) , 主要的缺陷機制是開路 , 因為會產生更多的過孔 , ” 安晟培(Ampere)研究員、負責 Chiplet 互連測試和修復標準化的 IEEE P3405 工作組主席斯里吉特?查克拉瓦蒂(Sreejit Chakravarty)表示 , “因此 , 主要會遇到單 lane 故障 。 再看采用微凸點(間距小至 25 微米)的硅中介層 , 短路比開路更常見 。 會看到焊料凸點融合 , 導致相鄰的兩條 lane 短路 。 而在混合鍵合中 , 灰塵顆粒或某種雜質可能會進入兩個表面之間 , 那么該灰塵顆粒周圍的大量連接都無法正常形成 。 故障會成簇出現 , 影響兩個以上的凸點 。 ”

過度翹曲和凸點 / 焊盤工藝偏差也可能影響多個連接點 , 尤其是在芯片和晶圓邊緣 。 這些可能會導致多個開路或虛焊接觸 , 最終在使用現場發生故障 。

lane 替換細節每個 Chiplet 的 I/O 以及 I/O 之間的互連構成一條 lane 。 lane 修復就是針對制造缺陷和現場故障替換有問題的 lane 。

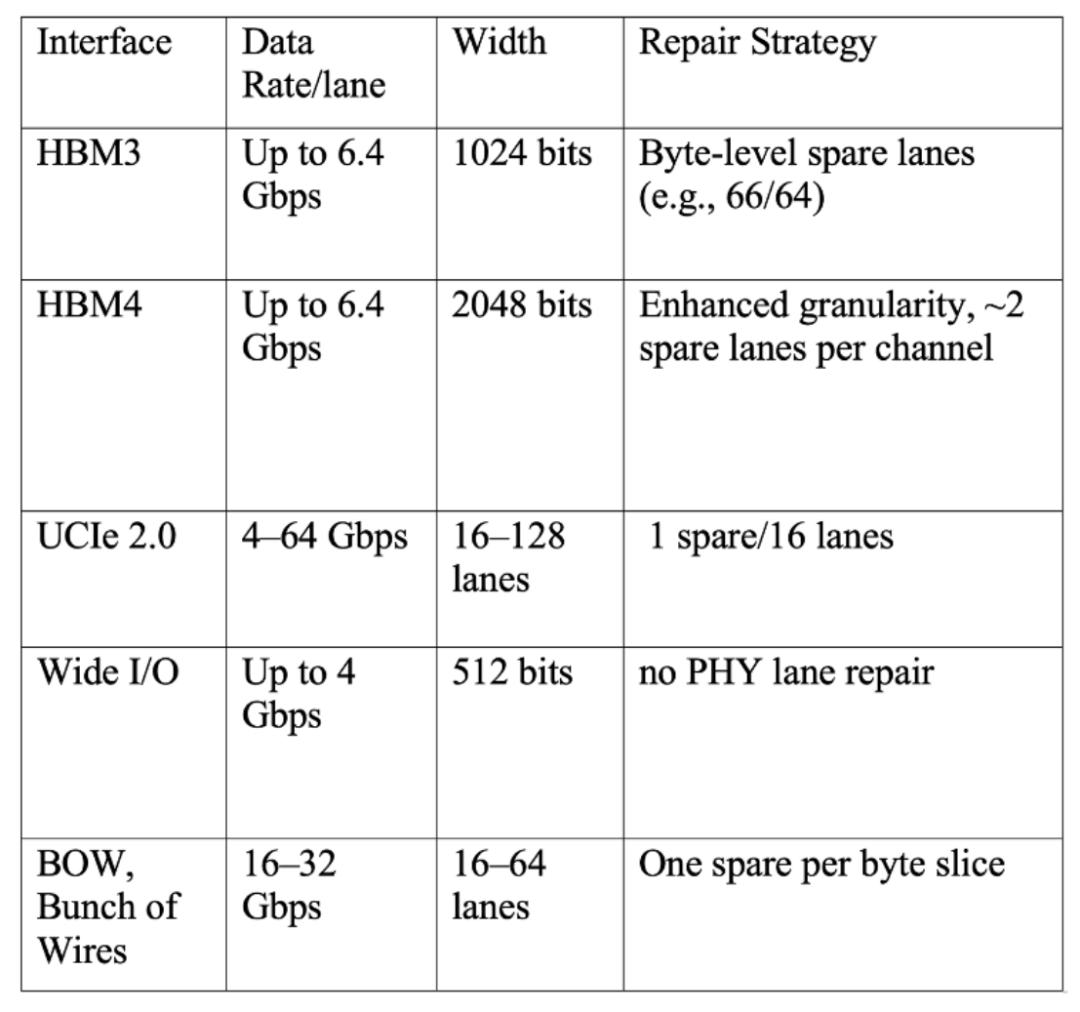

不同的 Chiplet 接口標準在信號與備用 lane 的比例上存在差異 。

表 1:Chiplet 接口及其修復策略 。 來源:愛德萬測試(Advantest)

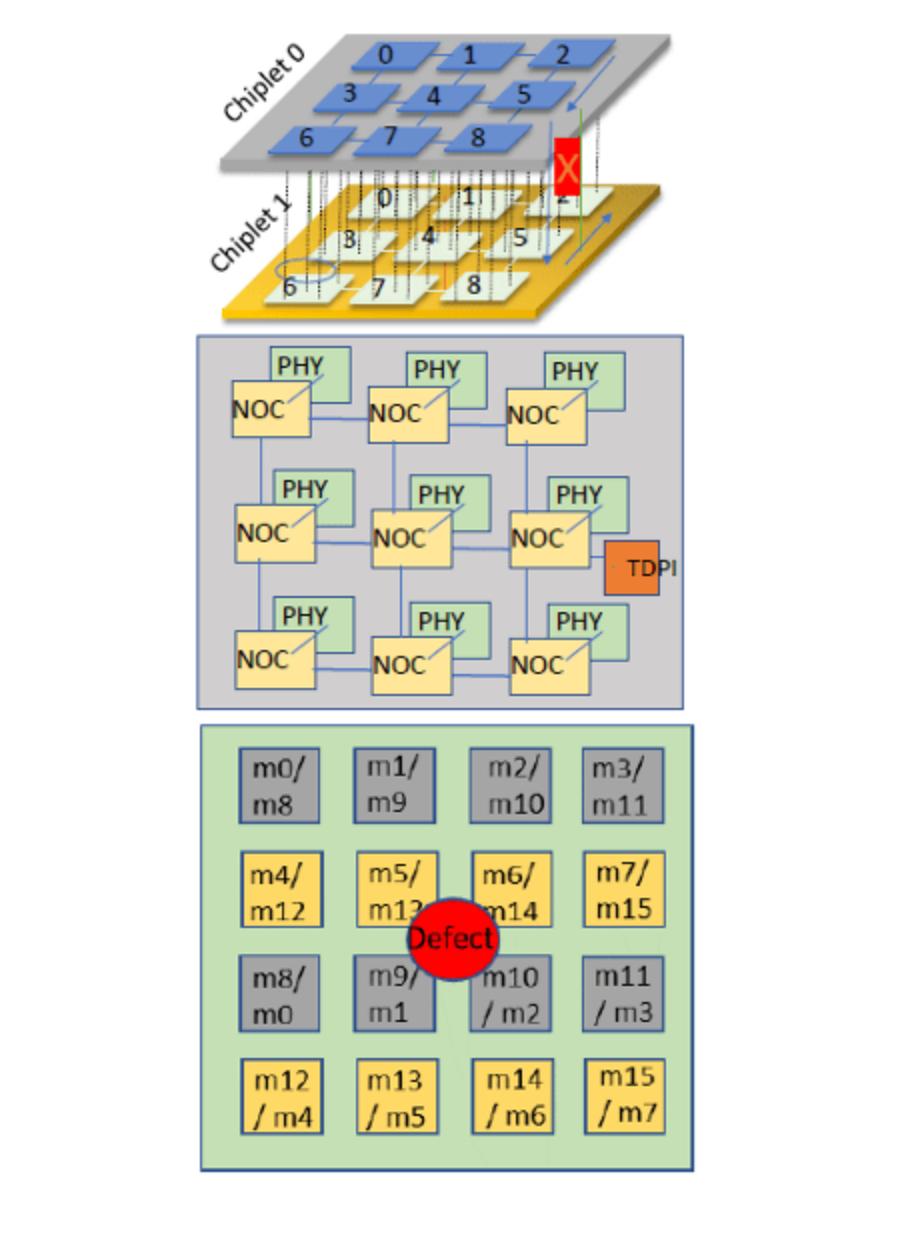

“多芯片設計中另一個重要的考慮因素是 , lane 偏移必須在兩個芯片中都實現 , ” 新思科技的戈里亞瓦拉表示 , “有故障的 lane 輸出 I/O 隨后會進入待機模式 。 對于數據中心 / 高性能計算和汽車等多芯片 IC 應用來說 , 這些都是重要的要求 , 因為從降低總擁有成本或安全性的角度來看 , 它們需要高可靠性 。 ”

圖 1:多芯片系統中的冗余 lane 。 來源:新思科技

對于 HBM 接口 , 研究團隊仍在探索各種修復方案 。 在最近的一篇論文中 , 作者強調需要考慮成簇的 I/O 故障 。 雖然在出現成簇故障時可以采用優雅降級方案 , 但這會導致數據帶寬顯著降低 。

需要具備應對堆疊芯片場景中成簇故障的能力 。

擬議的 UCIe 3D 標準考慮到了故障成簇的情況 。 這對于采用混合鍵合的組裝工藝來說非常重要 , 因為 5 至 10 微米的間距增加了兩個以上混合焊盤受到顆粒影響的可能性 。

圖 2:組裝缺陷可能影響 3D 芯片堆疊中的多個連接 。 來源:UCIe 聯盟

為有效應對這種情況 , 該標準將建議焊盤和 I/O 布局采用模塊化設計 。 在去年的一次演講中 , UCIe 聯盟主席、英特爾高級研究員德本德拉?達斯?夏爾馬(Debendra Das Sharma)討論了這種方法 , 他指出一個缺陷可能會影響 5×5 的凸點 / 焊盤區域 。 因此 , UCIe 3.0 架構將設計成帶有可用于修復的 I/O 模塊 , 以及隨后重新路由至冗余模塊的功能 。

具體細節描述如下:

UCIe3D:每個模塊有一個發射(TX)束(64 個 TX + 時鐘)和一個接收(RX)束(64 個 RX + 時鐘);

對于 9 微米的凸點間距 , 束布局大致為正方形 , 約 100 微米 ×100 微米;

【Chiplet 接口設計主動應對故障】對于密集排列的 2D UCIe 模塊陣列 , 預留兩個完整模塊(四個束)以修復一個故障簇;

假設在至少一個方向上發射束和接收束交替排列 。

圖 3:以束為單位的 UCIe 修復模塊化 , 展示了未修復的行、一個束有缺陷時修復的行、一個缺陷影響四個模塊時修復的兩行 。 來源:UCIe 聯盟

盡管如此 , 要充分實現異構集成 , 在不披露 Chiplet 專有內部設計的情況下實現 Chiplet 之間的連接 , 需要一種標準化的方法來測試 I/O 并修復 Chiplet 之間的連接 。

“如果購買的 Chiplet 帶有 UCIe 或 HBM 接口 , 那么你會了解其標準協議 , ” 西門子 EDA 泰森特(Tessent)產品總監維迪亞?尼爾昆達(Vidya Neerkundar)表示 , “我該如何連接它?如何測試它?如何進行 lane 修復?現有的 Chiplet 互連標準都內置了用于這些操作的機制 。 但如今 , 當不知道另一個芯片的預期時 , 兩個芯片之間的 I/O 沒有標準流程 。 而 P3405 是一個擬議的標準 , 旨在解決這些情況下的 I/O 測試和修復問題 。 ”

P3405 對于實現互操作性至關重要 , 從而實現來自不同來源的 Chiplet 的集成 。 如果沒有支持 Chiplet 之間 I/O 測試和修復的標準 , 這種集成就無法實現 。 P3405 定義了一種 I/O 測試和修復架構 , 用于驗證 I/O 連接是否需要更換并執行修復操作 。 它還將應對成簇 I/O 故障的實際情況 。

“未來兩年 , 高性能計算(HPC)將繼續主導大多數 2.5D 和 3D 硅設計 , ” 愛德萬測試美國公司測試技術銷售總監鮑勃?巴特利特(Bob Bartlett)表示 , “對于 I/O 修復 , UCIe 和 HBM 足以推動異構集成 , 因為我們正開始采用更多的 3D 封裝 。 但我認為這不再是測試成本的問題 , 而是良率成本的問題 。 當 3D 領域的所有設計工具都變得更好時 , 我們就能擁有成本更低的 3D 產品 。 這些產品將支持更多樣化的應用 , 與高性能計算產品相比 , 它們更小、更簡單且功耗更低 。 而對于 I/O lane 修復 , P3405 能夠支持這些低成本應用 。 ”

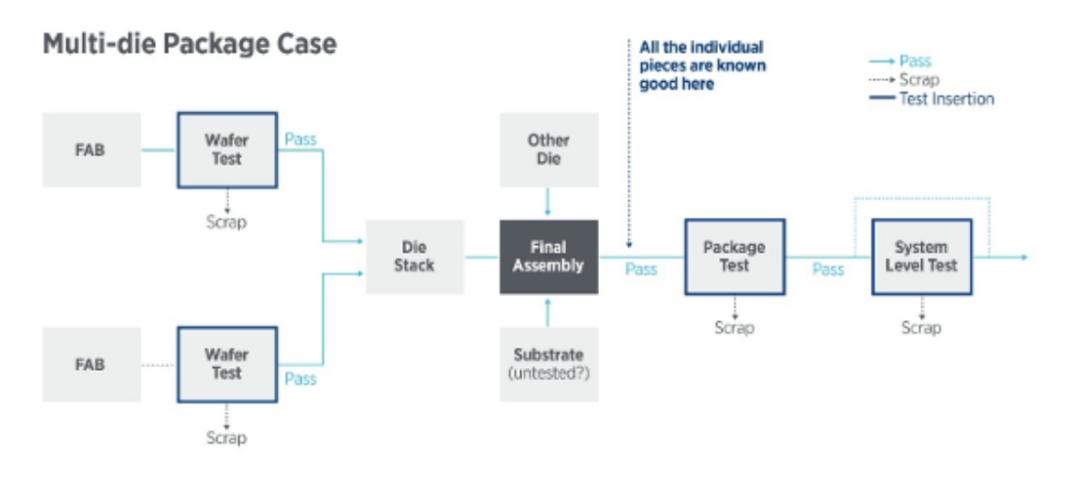

制造測試實施測試可確定需要修復的 lane 。 每種冗余方案都會影響測試程序以及從晶圓到系統測試的測試插入 。 考慮到這一點 , 工程團隊實施的實際測試流程可能會有所不同 。

“成本和質量始終是測試流程決策的驅動因素 , ” 泰克達因(Teradyne)首席技術專家兼戰略業務發展總監肯?拉尼爾(Ken Lanier)解釋道 , “在其他條件相同的情況下 , 平衡報廢成本與測試成本 , 以實現最低的制造成本 , 這始終會決定在每個插入點(傳統上是探針測試、封裝測試、系統級測試和最終產品測試)要進行哪些測試 。 先進封裝往往會使情況變得復雜 。 例如 , 芯片級封裝、存儲器堆疊和一般的多 Chiplet 封裝 , 要么會使某些插入點的測試無法進行 , 要么會促使針對后期制造步驟中引入的故障進行測試 。 ”

圖 4:基于 Chiplet 的產品測試流程 。 來源:泰克達因

Chiplet 接口的晶圓測試和封裝測試都需要可測試性設計(DFT)來提供訪問和測試內容 。 在晶圓測試中 , 并非所有芯片的微凸點都會被探測 , 通常只探測測試焊盤 。 一旦完成組裝 , 就無法通過自動測試設備(ATE)直接接觸 Chiplet 接口 。 組裝后的 I/O 測試需要包含針對橋接和開路缺陷的圖形覆蓋 。 由于凸點間距小且數據速率高 , 需要用適當的測試圖形來激活耦合和串擾故障行為 。

圖 5:高性能計算多芯片產品及有限的測試訪問途徑 。 來源:泰克達因(Teradyne)

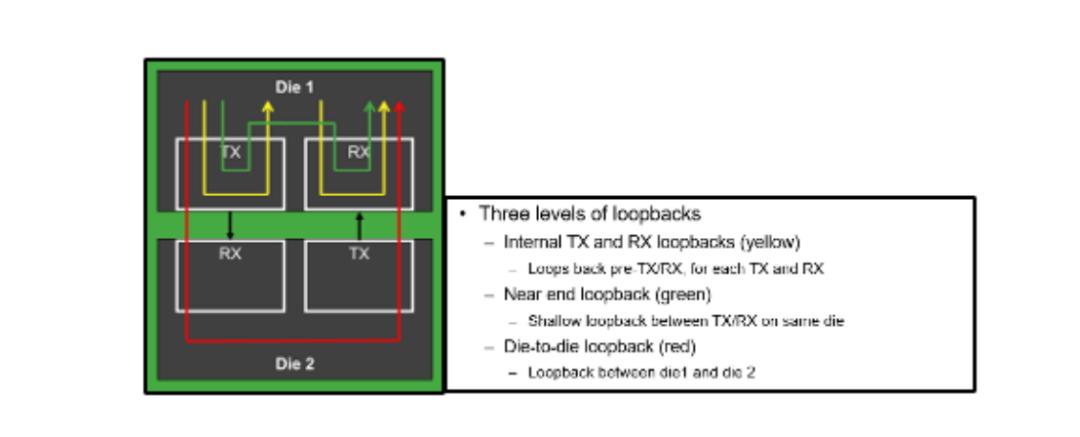

“在晶圓級測試中 , 會執行內部和近端環回內置自測試(BiST) , 以測試本地的發射(TX)和接收(RX)部分 , ” 新思科技(Synopsys)的戈里亞瓦拉(Goriawalla)表示 , “特別是在芯片與芯片鍵合后階段 , 需要執行遠端環回內置自測試和芯片到芯片內置自測試 , 以覆蓋兩個 Chiplet 的發射和接收部分 。 這些測試中表明存在缺陷 lane 的結果需要寫入物理層(PHY)的 lane 修復寄存器 , 并在不同的工藝、電壓和溫度(PVT)角落進行匯總 , 以便將最終的修復特征編程到本地的電子熔絲(e-fuse)/ 一次性可編程(OTP)元件中 。 對于后續的上電自檢(POST) , 額外的步驟是我們需要先加載修復特征(在運行測試之前) , 以確保已知的缺陷 lane 無需重新測試 。 ”

圖 6:三種類型的 I/O 環回 。 來源:新思科技

至于 I/O lane 修復是否應在晶圓級測試時進行 , 這要視情況而定 。 如果主要的 I/O 互連故障與組裝相關 —— 例如近端環回或直流測試中出現的 I/O 故障 , 芯片可能會被標記為不良品 , 但并非總是如此 。

“這完全取決于你希望最終測試達到多少良率 , ” 查克拉瓦蒂(Chakravarty)說 , “如果整個修復流程的良率很低 , 那么你可以考慮在晶圓測試時修復芯片 。 這種選擇需要以數據為依據 , 因為你還需要組裝芯片并測試封裝后的產品 。 ”

如果客戶要求在晶圓級測試時進行 I/O 修復 , 那么這會增加芯片的屬性 , 以便將具有相似特征的芯片進行匹配 。 有關已修復 / 已替換 lane 的信息存儲在電子熔絲 / 非易失性存儲器(e-fuse/NVM)中 , 這使得匹配成為可能 。

“lane 修復信息存儲在設備中 , 只要設備被重新配置為使用一定數量的冗余 lane(如果有的話)用于芯片到芯片接口 , ” 泰克達因的拉尼爾(Lanier)解釋道 , “有趣的是 , 現在封裝過程需要確保與已修復芯片相連的任何芯片都有一組匹配的可用 lane 。 這是基于 Chiplet 的設備在芯片匹配這一整體問題中的一個方面 。 ”

在替換之前 , 是否將冗余 lane 的測試作為測試過程的一部分 , 取決于客戶需求 。 用于汽車、航空航天和其他安全關鍵應用的多芯片產品將需要對所有備用 lane 進行預測試 。

“假設我們有 30 條 lane 和 2 條備用 lane , ” 查克拉瓦蒂說 , “最初 , I/O 內置自測試將測試 30 條 lane 。 測試結束時 , 發現第 17 條 lane 有問題 。 內置自測試會將該信息提供給多路復用邏輯 , 用其中一條冗余鏈路替換第 17 條 lane 。 接下來 , 會重新運行 I/O 內置自測試序列 , 以確保連接良好 。 但對于大量的冗余 lane , 客戶可能要求測試冗余 lane 是否正常工作 , 這可能需要在所有測試插入點進行 , 還需要在老化測試期間對冗余電路進行測試 。 ”

I/O 替換也可以在現場進行 , 以應對基于可靠性或老化的故障 。 當設備在測試流程結束時用盡所有備用 lane 時 , 這給設備制造商帶來了一個難題 。 設備仍然可以運行 , 但沒有備用 lane 了 。 一種可能的做法是根據剩余備用 lane 的數量對設備進行分檔 。

“這是一個很好的問題 , 因為根據修復 lane 的數量對部件進行分檔可能是有價值的 , ” 安靠科技(Amkor Technology)的制造測試技術專家維尼特?潘喬利(Vineet Pancholi)說 , “在技術不斷成熟的過程中 , 這可能很重要 。 我們尚未觀察到客戶針對高性能計算和汽車領域的產品 , 根據制造后可用的修復 lane 數量對部件進行分檔 。 一旦有足夠的數據證明現場修復需求的好處 , 這種情況可能會改變 。 ”

泰克達因的拉尼爾對此表示贊同:“這取決于具體情況 。 如果是外部接口 , 或許你仍然可以將最終設備作為較低性能的版本出售 。 對于內部(芯片到芯片)總線 , 情況似乎也是如此 , 但這聽起來確實很難管理 。 ”

結論就像存儲器設備設計人員接受了位單元故障的現實一樣 , 多芯片設備設計人員也在接受 lane 故障的現實 。 隨著 Chiplet 互連數量達到數十萬 , I/O 測試以及隨后通過替換備用 lane 進行修復的做法將變得更加普遍 。

“這一切都歸結為缺陷密度 , ” 愛德萬測試(Advantest)的巴特利特(Bartlett)說 , “組裝觸點、微凸點、焊盤 —— 所有東西都在變得更小 。 混合鍵合的間距已達到 10 微米 , 并正朝著 5 微米邁進 。 你的 I/O 接口需要堅固耐用 。 你需要足夠的可修復性 , 以確保設備能正常工作 10 年 。 而且 , 隨著不斷縮小 , 你將需要更多的修復能力 。 ”

或者簡單地說 , 為了提高組裝后的良率 , 冗余 lane 的需求已成為必要 。

*聲明:本文系原作者創作 。 文章內容系其個人觀點 , 我方轉載僅為分享與討論 , 不代表我方贊成或認同 , 如有異議 , 請聯系后臺 。

想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 徹底解開封印!紅米新機迎來USB3接口,但這些升級更實在

- 蘋果新機曝光,設計大改!

- iPhone 17 Pro 新設計曝光,信號變好了?

- 蘋果 HomePod mini 2 即將發布,新設計首次曝光

- 榮耀Magic8系列突然入網:直屏設計+90W有線快充,多款機型蓄勢待發

- 奧特曼公然叫板馬斯克,重金殺入腦機接口,硅谷兩大巨頭徹底決裂

- 華為Mate80驚艷曝光:設計新高度,看完后直接點贊

- 榮耀 Magic V2 官宣:晨曦紫設計驚艷亮相,豎向折疊新風尚來襲!

- 阿爾特曼,要做腦機接口了

- OpenAI和奧特曼將投資一家腦機接口公司,直接與Neuralink競爭