文章圖片

文章圖片

DRAM制程如何突破 10nm?這曾是困擾行業的共同課題 。

近日 , SK海力士帶來了它的答案 。

本周 , 2025年IEEE VLSI 研討會在日本東京舉行 , 會議上SK海力士提出了未來30年的新 DRAM 技術路線圖 。

SK 海力士表示 , 4F2 VG和3D DRAM技術將應用于10nm及以下級內存 。

至于10nm DRAM如何成為制程技術的難點?未來30年DRAM市場為什么依賴3D?4F2 VG技術又是什么?筆者在下文一一說明 。

011c DRAM , 龍頭齊聚

一直以來 , 各大內存廠商將上一代DRAM芯片按照1X、1Y、1Z進行工藝區分 , 1Xnm工藝相當于16-19nm制程工藝、1Ynm相當于14-16nm制程工藝 , 1Znm工藝相當于12-14nm制程工藝 。 而新一代的1a、1b和1c則分別代表14-12nm、12-10nm以及10nm及以下制程工藝 。

為什么說10nm , 是DRAM技術進程中的絆腳石?

隨著10nm制程的臨近 , 使其在晶圓上定義電路圖案已經接近基本物理定律的極限 。 由于工藝完整性、成本、單元泄漏、電容、刷新管理和傳感裕度等方面的挑戰 , DRAM存儲單元的縮放正在放緩 。

法國分析機構Yole指出 , 即使通過光刻EUV 工藝 , 平面縮放也不足以在整個下一個十年提供所需的位密度改進 。

1c DRAM及接下來的發展很難 , 但這扇大門已被存儲三大原廠叩響 。

去年8月 , SK海力士宣布完成第六代10nm級(1c)工藝DRAM 開發 。 當時SK海力士就曾強調:隨著10nm級DRAM技術的世代相傳 , 微細工藝的難度也隨之加大 。 其中需要注意的一個點是 , 早在2021年SK海力士就已經開始將EUV應用于其10nm級第四代DRAM 。

今年2月 , 美光宣布已向生態系統合作伙伴及特定客戶出貨專為下一代 CPU 設計的 1γ(1-gamma)第六代(10 納米級)DRAM 節點 DDR5 內存樣品 。

三星的第六代10納米級1c DRAM制程開發進度出現了延遲 , 預計完成時間從2024年年底推遲至2025年6月 。 這也意味著 , 本月或許就能看到三星新成果的推出 。

【DRAM,開啟30年“新賭局”】此前韓媒報道 , 在下一代的HBM4內存開發上 , 三星和SK海力士正計劃使用1c制程的DRAM 。

而隨著1c納米制程DRAM 商業化 , EUV光刻制造成本將快速攀升 。 現在來看 , 1c DRAM技術的發展似乎變得緊迫起來 。 接下來該怎么走?如何走?

3D DRAM便是那個最被看好的選手 。

3D DRAM可降低成本、最大限度地降低功耗并提高速度 。

SK 海力士表示 , 采用VG 或3D DRAM 制程設計 , 可將EUV 制程成本降一半 。

上圖可見 , 再往后的10nm以下節點 , 將分別命名為0a、0b、0c、0d , 其中打頭的0a工藝預計2027年底-2028年初量產(月產能超過2萬塊晶圓) , 0d則要到2032年 。

如果說2030年DRAM市場將高度依賴3D , 毫不夸張 。

那么 , 4F2 VG DRAM技術又是什么?

4F2 VG DRAM的設計靈感來源于NAND閃存 , 采用了混合鍵合技術 。 這是一種經過大量研究的單元陣列結構 , 其中晶體管以垂直方式堆疊 , 也就是3D DRAM 。 三星將這種3D DRAM 稱為“垂直通道晶體管”(vertical channel transistor , 簡稱VCT) 。

4F2結構從下而上依序為源極(source)、閘極(gate)、汲極(drain)和電容器(capacitor) 。 字元線(Word Line)連接到閘極 , 位元線(Bit Line)則連接到源極 。

4F2 VG 將傳統 DRAM 中的平面柵極結構調整為垂直方向 , 可最大限度減少單一數據存儲單元的面積占用 , 同時有助于實現高集成度、高速度和低功耗 。

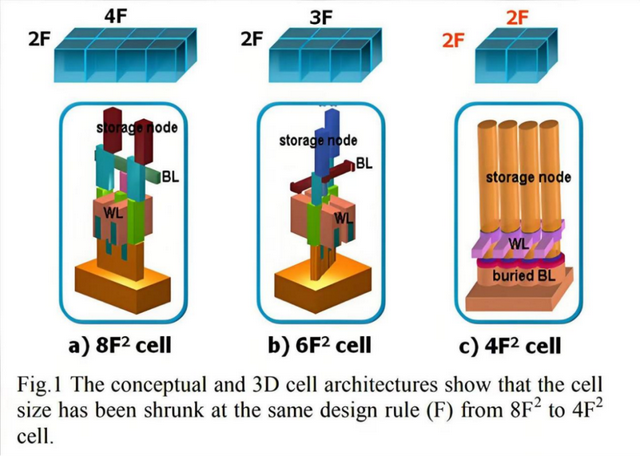

那么4F2是如何由來的呢?是否存在6F2和8F2?是的 。

8F2 :如上圖所示 , 早期DRAM采用8F2 RCAT結構 , 位線跨4格 , 字線跨2格 , 總面積8F2(F為最小特征尺寸) , 但源極無法直接與字線連接 , 需留白 , 單元實際占4格位線寬度 。 雖結構簡單 , 位線與字線留白卻限制存儲密度提升 。

6F2 :自130納米及以下制程起 , 6F2 BCAT結構登場 , 單元布局優化為位線3格、字線2格 , 大幅提升單元密度 。 然而 , 隨線路寬度縮小到10納米級 , 物理極限致電流泄漏、信號干擾頻發 , 平面棋盤格排列單元難以為繼 。

4F2:為高效利用有限面積 , 豎起水平排列單元或垂直堆疊單元陣列成必然選擇 。 4F2結構將源極、柵極、漏極轉為垂直結構 , 下層源極接位線 , 其上柵極連字線 , 再往上堆疊漏極與電容器 , 減少電氣干擾 , 面積縮小約30% 。

不過4F2結構的內存芯片早在10多年前就有研發了 , 剛進入DDR3時代就有廠商計劃使用 , 只是一直沒有取得實際的進展 , 制造難度也非常大 。

02三星 , 也緊盯4F2 DRAM

盯上4F2 DRAM的 , 可不只是SK海力士 。

早在2023年 , 三星就組建了一個開發團隊 , 目的是進一步推進4F2結構DRAM的應用 , 并將其量產應用于10納米以下的DRAM制程 。

三星電子表示 , 多家公司正致力于將技術過渡至4F2 垂直通道晶體管 DRAM , 但需要克服一些技術上的挑戰 , 包括開發氧化物通道材料和鐵電體等新材料 。 業內人士認為 , 三星計劃 2025 年即將推出的 4F2 DRAM 的首批樣品可能僅僅是內部發布試制樣品 。 半導體設備制造商東京電子則估計 , 采用 VCT 和 4F2 技術的 DRAM 將在 2027 年至 2028 年間問世 。

相較于在DRAM單元結構上向z方向發展的VCT DRAM , 三星電子還聚焦在VS-CAT(Vertical Stacked-Cell Array Transistor , 垂直堆疊單元陣列晶體管)DRAM上 , 該技術類似3D NAND一樣堆疊多層DRAM 。

除通過堆疊提升容量外 , VS-CAT DRAM 還能降低電流干擾 。 三星電子預計其將采用存儲單元和外圍邏輯單元分離的雙晶圓結構 , 因為延續傳統的單晶圓設計會帶來嚴重的面積開銷 。

在分別完成存儲單元晶圓和邏輯單元晶圓的生產后 , 需要進行晶圓對晶圓(W2W)混合鍵合 , 才能得到 VS-CAT DRAM成品 。

據悉 , 目前三星電子已在內部實現了16層堆疊的VS-CAT DRAM 。

03有了HBM , 就足夠了?

讀到這里 , 可能有讀者會問:HBM 不也是 3D DRAM 嗎?用HBM不就夠了嗎?為什么還要研究3D?答案是單單依賴HBM , 還存在不足 。

最直觀的兩點:1、HBM產量不足 。 2、HBM成本過高 。

通往3D DRAM , 主要有這樣兩條路徑 , HBM采用的是最直接的方法 , 垂直堆疊多個 DRAM 芯片 , 并使用硅通孔(TSV)技術垂直連接各層芯片 , 各層 DRAM 通過微凸點與邏輯芯片相連 。

常見的HBM芯片為4和8高以及16高 , 與基本 DRAM 相比 , 這是一種更昂貴的方法 , 因為在封裝中堆疊die需要付出努力 , 但對于需要大量附近內存的應用程序 , 如AI , 這是值得的 。

另一種方式是單片堆疊 DRAM , 將多個 DRAM 芯片堆疊在一起 , 但連接方式可能有所不同 。 部分單片堆疊技術采用混合鍵合技術 , 兩個晶圓的金屬鍵合焊盤以及相鄰介電材料直接連接 , 這種方式下沒有 HBM 結構中芯片之間的導電凸塊 , 且存儲器芯片厚度更薄 , 堆疊高度整體降低 。

作為一種自然延伸 , 單片堆疊芯片只需少量額外步驟 , 自然這少量的額外步驟也會導致很多困難 。

043D DRAM , 2030年見分曉

有機構預測 , 到2030 年 , 全球 3D DRAM 市場規模有望增長到 1000 億美元 。

正是看到了這樣的發展前景 , 以存儲芯片三巨頭為代表的廠商都在發力 , 進行相關技術和產品的研發 。 其中三星對該技術最為關注的 , 投入也最大 。

三星通過VCT技術將晶體管垂直排列 , 使單元面積縮小30% , 并結合鉿鋯氧化物(HZO)材料優化電荷存儲性能 。 目前其已成功研發128Gb容量的3D X-DRAM樣品 , 目標2030年前將單顆芯片容量擴展至1Tb 。

據悉 , 三星電子在美國硅谷開設了一個新的研發實驗室 , 主要進行3D DRAM 研發 。 據悉 , 該實驗室隸屬于硅谷的 Device Solutions America (DSA) 部門 , 負責監督三星電子在美國的半導體生產 , 并專注于新一代 DRAM 產品的開發 。

除了要在2025 年量產 , 三星電子還要在 2027~2028 年將相關制程節點縮小到 8nm~9nm , 目前 , 最先進的 DRAM 制程約為 12nm 。

SK海力士去年在“VLSI 2024”大會上展示了5層堆疊3D DRAM原型 , 并宣布實現了56.1%的良率 。

其研究論文 , 指出實驗中的3D DRAM顯示出與目前使用的2D DRAM相似的特性 , 這是海力士首次披露其3D DRAM開發的具體數據和運行特性 。 此外 , 海力士還在研究將IGZO材料應用于3D DRAM , 以解決帶寬和延遲方面的挑戰 。 IGZO是由銦、鎵、氧化鋅組成的金屬氧化物材料 , 大致分為非晶質IGZO和晶化IGZO 。

美光在2019年就開始了3D DRAM的研究工作 。 截止2022年8月 , 美光已獲得了30多項3D DRAM專利 。 相比之下 , 美光專利數量是三星和SK海力士這兩家韓國芯片制造商的兩三倍 。 美光于 2023 年末在 IEEE IEDM 會議上披露了其 32Gb 3D NVDRAM(非易失性 DRAM)研發成果 。 不過根據外媒 Blocks & Files 從兩位受采訪的行業分析師處得到的消息 , 這一突破性的新型內存基本不可能走向商業化量產道路 , 但其展現的技術進展有望出現在未來內存產品之中 。

除了大廠 , 有些創業公司也在進行3D DRAM 開發 。

例如 , 美國公司NEO Semiconductor 推出了一種名為 3D X-DRAM 的技術 , 旨在克服 DRAM 的容量限制 。 3D X-DRAM 的單元陣列結構類似于 3D NAND Flash , 采用了 FBC 技術 , 它可以通過添加層掩模形成垂直結構 , 從而實現高良率、低成本和顯著的密度提升 。

據NEO 介紹 , 3D X-DRAM 技術可以跨 230 層實現 128Gb 的密度 , 是當前 DRAM 密度的 8 倍 。 NEO 提出了每 10 年容量增加 8 倍的目標 , 計劃在 2030~2035 年實現 1Tb 的容量 , 比目前 DRAM 的容量增加 64 倍 。

想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 一粒「扣子」,開啟了Agent的全生命周期進化

- 人工智能的最佳DRAM

- LeCun世界模型出2代了,62小時搞定機器人訓練,開啟物理推理新時代

- 谷歌流量急墜歸0?核心員工被「自愿離職」,30年搜索帝國崩塌

- VC均熱板加持,獨顯14英寸全能本七彩虹源N14開啟預約

- HarmonyOS 5.1將于7月開啟升級!為你的設備注入全新升級體驗!

- 6月12日京東618電競驚喜日開啟 買鍵鼠享三重補貼至高優惠50%

- 32周年:奧拓電子如何以AI+視訊,開啟LED光顯新紀元

- 榮耀開啟“清倉模式”,從3999元跌至2379元,高配版已淪為中端機

- 負責人開啟“微博辦公”模式,小米下決心重整可穿戴產品線