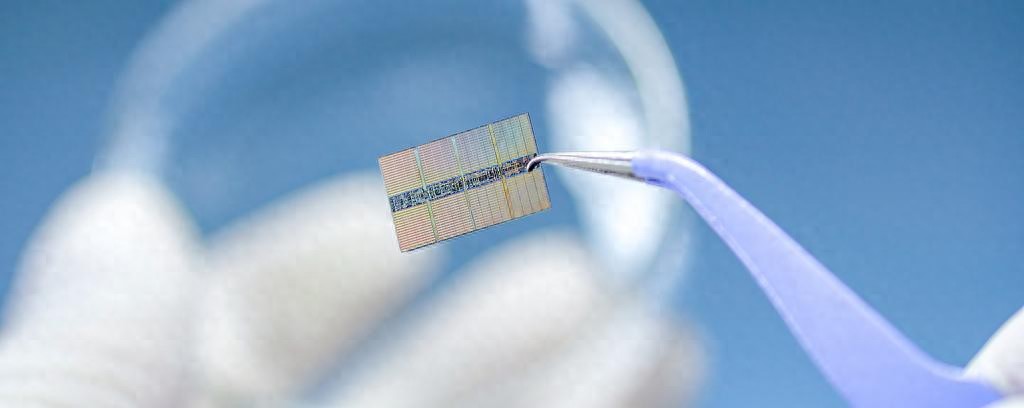

韓國半導體工程師學會(The Institute of Semiconductor Engineers)在其發布的《2026 年半導體技術路線圖》中 , 公布了未來 15 年硅基半導體技術的發展預測 。 三星近期才推出全球首款采用 2nm全環繞柵極(GAA)工藝的芯片 ——Exynos 2600 , 而路線圖預測 , 到 2040 年半導體電路制程將突破至 0.2nm , 正式邁入埃米時代 。 不過 , 從當前到未來的十五年多時間里 , 行業需實現跨越式突破 , 通往亞1納米晶圓制程的道路上 , 仍橫亙著諸多瓶頸與阻礙 。

據報道 , 該技術路線圖的制定目的在于助力提升半導體領域的長期技術與產業競爭力、推動學術研究創新、完善人才培養戰略 。 韓國半導體工程師學會發布的這份路線圖 , 涵蓋九大核心技術領域 , 具體包括:半導體器件與工藝、人工智能半導體、光互連半導體、無線互連半導體傳感器、有線互連半導體、功率集成電路模塊、先進封裝以及量子計算 。

據悉 , 三星電子已經規劃了2nm GAA的升級版本 , 不僅完成了第二代 2nm GAA 工藝節點的基礎設計 , 還計劃在兩年內落地第三代 2nm GAA 技術 , 即 SF2P + 工藝 。 路線圖預計 , 到 2040 年 , 0.2nm制程將采用CFET這一全新晶體管架構 , 并搭配單片式3D設計 。

三星已組建專項團隊 , 啟動 1 納米芯片的研發工作 , 目標在 2029 年實現量產 。 這些制程工藝的升級成果 , 不僅將應用于SoC , 還將覆蓋DRAM領域 , 其存儲電路制程將從 11 納米縮減至 6 納米;HBM也將迎來技術迭代 , 堆疊層數從 12 層提升至 30 層 , 帶寬則從 2TB/s 躍升至 128TB/s 。

在 NAND 閃存領域 , SK 海力士已研發出 321 層QLC技術 , 而根據路線圖預測 , 未來半導體技術的進步將推動 QLC NAND 閃存的堆疊層數突破至 2000 層 。

在人工智能處理器方面 , 當前芯片的運算能力可達每秒 10 萬億次操作(10 TOPS) , 而這份報告指出 , 十五年后 , 用于模型訓練的 AI 芯片運算能力有望達到每秒 1000 萬億次操作(1000 TOPS) , 用于推理任務的芯片運算能力也將提升至每秒 100 萬億次操作(100 TOPS) 。

值得一提的是 , 韓國產業通商資源部近日表示 , 政府明年將投入7000億韓元(約合4.78億美元) , 支持制造業的人工智能(AI)轉型項目 , 包括設備上AI芯片的開發和AI工廠的出口 。 由政府主導的制造業人工智能轉型企業和團體組成的“制造業人工智能聯盟(M.AX)” , 在第一次總會上公布了明年的五大項目 。

【韓國半導體工程師學會:到2040年芯片制程將突破至0.2納米】這些項目包括開發機器人、汽車和人工智能工廠的AI模型、開發設備上的AI芯片、促進人工智能工廠的出口 。 具體來說 , 政府計劃到2030年至少投資1000億韓元 , 用于建立制造業的AI數據庫 , 到2032年再投資7000億韓元 , 用于開發人工智能工廠、未來移動、AI機器人的定制AI模型 。

該聯盟的目標是開發用于汽車、機器人、家電的設備上AI芯片 , 到2028年發布試驗產品 , 到2030年開發出10種AI半導體 。 具體目標是2029年實現人形機器人的量產 , 2030年實現自動駕駛汽車的量產 , 并希望通過核心制造業的人工智能轉型 , 到2030年創造100萬億韓元以上的附加價值 。

想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 三星電子G2氣體,可用于半導體蝕刻工藝

- 專訪戴森首席工程師 Jake Dyson:在快節奏的時代,堅持做困難的事情

- AI浪潮之下,美國第一個贏麻了,韓國第二個贏麻了

- AI搶產能,內存漲價潮。

- TC Bonder市場,韓美半導體71.2%領跑

- 字節TRAE,正悄悄“解放”600萬工程師

- 字節 92% 工程師都在用的 TRAE,這次瞄準了企業級市場

- 半導體十大預測,“進度條”幾何?

- 韓國半導體,靠著存儲二次復興

- 抑制創新,利好日本?韓國或將成為全球首個實施全面AI監管的國家