文章圖片

文章圖片

共封裝光學(CPO)技術是下一代數據中心架構的核心使能技術 , 通過將光引擎與交換芯片緊密集成 , 有望實現前所未有的帶寬密度和能效 。 然而 , 這項下一代光互連技術誕生已近十年 , 其大規模商業化落地目前處于何種階段?

在深入探討CPO的技術路線圖及其未來部署前景之前 , 我們先對這一硅光架構進行簡要介紹 , 看看它是如何為AI、HPC和高速網絡應用提供助力 。

CPO 技術將光學組件直接集成于單一封裝內 , 可最大限度縮短電信號傳輸路徑 , 顯著降低信號損耗、提升高速信號完整性 , 并有效控制延遲 。 換言之 , CPO 通過采用高帶寬光引擎提升數據吞吐量 , 與傳統銅纜連接相比 , 光引擎不僅能實現更高的數據傳輸速率 , 還不易受電磁干擾(EMI)影響 。

此外 , 這種硅光集成技術通過減少對高功耗電驅動器、中繼器和重定時器的需求 , 進一步提升了能效 。 通過縮短銅質走線長度 , CPO 可大幅優化鏈路預算 , 甚至無需數字信號處理器(DSP)或重定時器功能 。 這將顯著降低每比特數據的整體功耗 , 而這也正是AI數據中心管理中的一項核心關鍵指標 。

2025年CPO有哪些關鍵進展?2025年1月 , Marvell宣布其定制化 XPU 架構與CPO技術的集成取得重大突破 。 該公司展示了其定制化 AI 加速器架構如何通過SerDes、芯片間接口及先進封裝技術 , 將 XPU 計算芯片、高帶寬內存(HBM)及其他芯粒與 3D 硅光引擎集成于同一襯底之上 。

這一設計使得電信號無需離開 XPU 封裝即可傳輸至銅纜或PCB之外 。 此外 , XPU 之間的連接不僅能實現更快的數據傳輸速率 , 傳輸距離也可達銅纜連接的 100 倍 。 Marvell的 3D 硅光引擎支持 200 Gbps 的電接口和光接口速率 。

Marvell網絡交換業務部高級副總裁兼總經理Nick Kucharewski表示:“AI 擴展型服務器需要更高的信號傳輸速率和更遠的傳輸距離 , 以支持前所未有的 XPU 集群規模 。 將共封裝光學技術集成到定制化 XPU 中 , 是通過更高的互連帶寬和更遠的傳輸距離實現性能擴展的必然下一步 。 ”

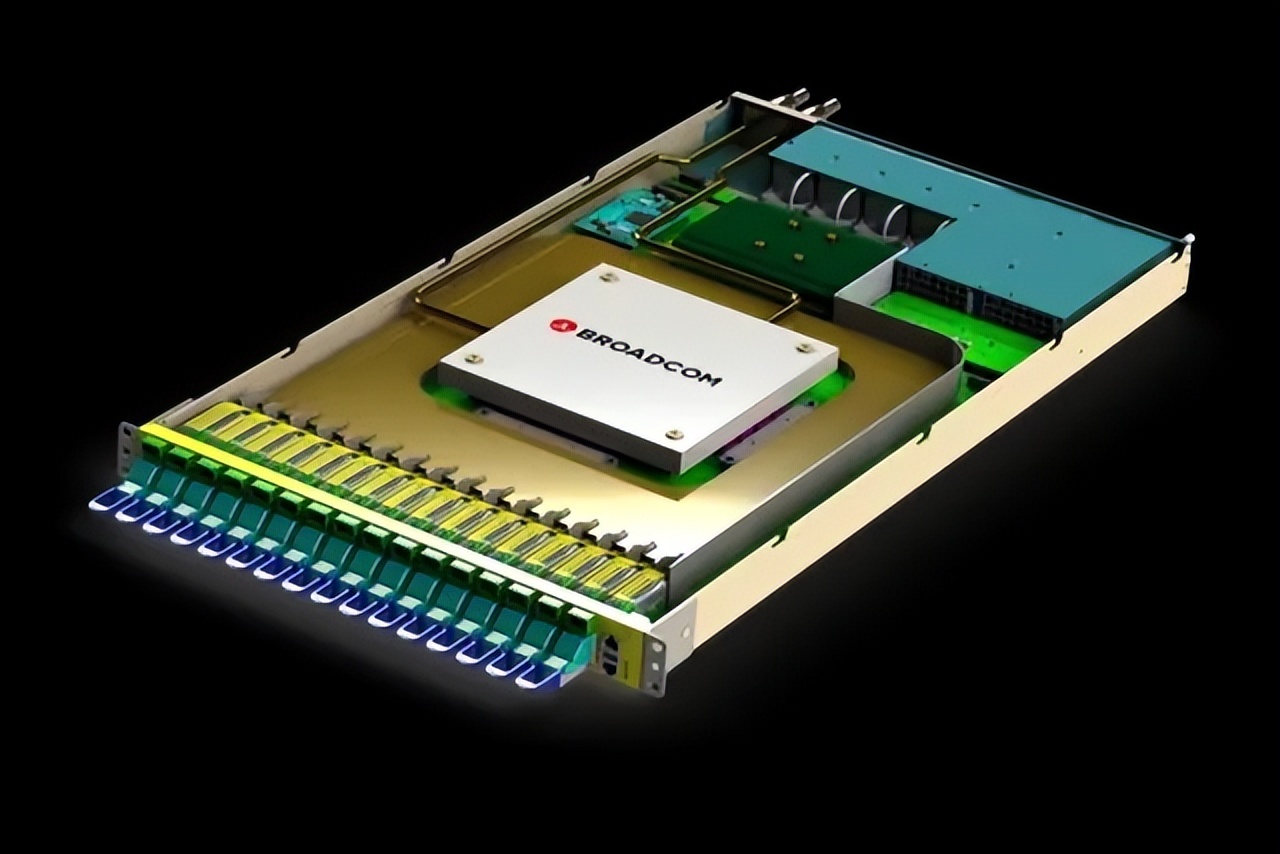

2025年5月 , 博通首次展示了其第三代每通道 200G 速率的CPO技術 。 博通的CPO研發之路始于 2021 年的 Tomahawk 4-Humboldt 芯片組 , 而其第二代產品 Tomahawk 5-Bailly 芯片組則成為業內首款實現量產的CPO解決方案 。

博通光學系統事業部副總裁兼總經理Near Margalit表示:“博通已投入多年時間來完善CPO平臺解決方案 , 第二代每通道 100G 產品的成熟度及生態系統的就緒程度便是最好的證明 。 ” 該公司還聲稱 , 除了邊緣交換機 ASIC 和光引擎技術外 , 其還擁有涵蓋無源光學組件、互連產品及系統解決方案合作伙伴的完整生態系統 。

2025年10月 , 博通宣布 , Meta在高溫實驗室環境下對其CPO解決方案進行了總計 100 萬鏈路小時的測試 , 期間未出現任何一次鏈路閃斷 。 鏈路閃斷指的是短暫的連接中斷 , 是高性能數據中心網絡中一項關鍵的可靠性指標 。

除了博通、Marvell等CPO行業巨頭外 , 硅光領域也有不少值得關注的初創企業在致力于攻克I/O瓶頸 。 例如 , 光互連解決方案供應商Ayar Labs已將其 TeraPHY 光引擎整合至芯片設計企業GUC的 ASIC 設計服務中 。

2025年11月 , Ayar Labs宣布 , 其已將光引擎集成到GUC的先進封裝和 ASIC 設計流程中 , 這是邁向未來CPO部署的關鍵一步 。 雙方的聯合設計工作有助于解決CPO集成過程中的核心挑戰 , 包括架構設計、功耗與信號完整性、機械設計以及熱管理等問題 。

Ayar Labs首席技術官兼聯合創始人Vladimir Stojanovic表示:“如果沒有光學技術來攻克電 I/O 瓶頸 , 未來的 AI 和數據中心規模擴展將無從談起 。 與GUC在先進封裝和硅技術領域展開合作 , 是展示光引擎如何幫助超大規模數據中心運營商和 AI 擴展型企業加速共封裝光學技術落地的重要一步 。 ”

CPO技術未來如何發展?盡管CPO技術的支持者迫切宣稱CPO革命已近在眼前 , 但法國市場研究機構Yole Group等行業觀察家認為 , 大規模部署要等到 2028 至 2030 年才會實現 。 在此期間 , 插裝在 PCB 邊緣交換機前面板的可插拔光模塊仍將保持競爭力 。

市場研究機構LightCounting也預測 , 在未來十年內 , 光模塊仍將占據數據中心光鏈路的主導地位 。 不過 , 與此同時 , 光收發器技術也將持續穩步向 “光學組件靠近 ASIC” 的方向演進 。

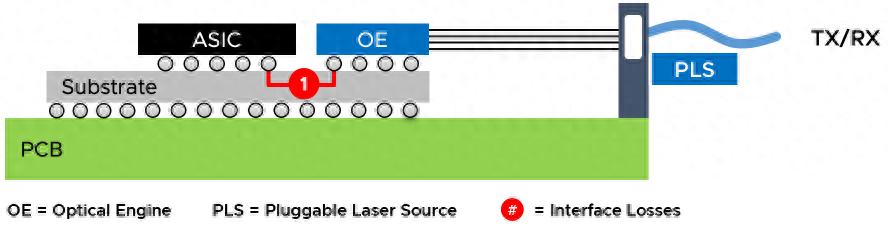

這是因為 , 隨著交換機 ASIC 與光引擎之間的銅質走線長度不斷增加 , 傳統可插拔光模塊在信號損耗、功耗和延遲方面正面臨越來越大的限制 。 而CPO技術通過將光引擎放置在更靠近交換芯片的位置 , 成功克服了這些局限性 。

光引擎向交換機 ASIC 的靠近 , 縮短了電信號傳輸所用銅質走線的長度 , 從而提升了電性能 。 然而 , 要將光引擎無縫集成到交換機 ASIC 或 XPU 中 , 需要多種封裝技術的支持 , 包括 2.5D 中介層、硅通孔(TSV)、扇出型晶圓級封裝 , 以及通過混合鍵合實現的 3D 集成技術 。

隨著這些先進封裝技術的穩步發展 , CPO 的部署進程也在持續推進 。 英國市場研究機構 IDTechEx 預測 , 到 2036 年 , 全球CPO市場規模將超過 200 億美元 , 2026 至 2036 年期間的復合年增長率(CAGR)將高達 37% 。

【2026年,CPO將如何發展?】想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 聯想moto X70 Air Pro AI手機預熱,即將發布

- Linux 在 2026 年將勢不可擋,但一個開源傳奇可能難以為繼

- 宇樹科技線下首店開業,CMO王其鑫:拉近用戶距離,明年還將繼續開店

- 三星開發SbS新型封裝技術,Exynos 2700將率先采用

- 定了,一文讀懂2026年國補政策

- 2026年國補來了 1月1日起上淘寶天貓領取,家電數碼補貼15%

- 增程七座SUV和改款SU7全都有 小米汽車2026年將推出4款新車

- 智創未來,玩出新生!HKC惠科股份將攜旗下三大品牌亮相CES 2026!

- 英偉達50億美元入股英特爾 AMD將迎最強對手

- 英偉達斥資50億美元收購英特爾股份,RTX GPU將集成至Intel處理器