文章圖片

本文由半導體產業縱橫(ID:ICVIEWS)編譯自semiengineering

面向制造的系統設計將芯片、中介層、封裝和分析視為一個單一的、連貫的系統 。

隨著先進工藝節點的擴展日益受到成本、良率和功率密度的限制 , 半導體創新正果斷地轉向3D集成電路 技術、芯片組和異構集成 。 在人工智能基礎設施、云計算、汽車電子和高性能系統等領域 , 設計團隊正超越單片SoC , 通過先進的封裝技術釋放更高水平的性能、效率和可擴展性 。

本文匯總了源自實際生產部署的Cadence 3D-IC案例研究 。 這些案例重點展示了帶寬、能效、可靠性和流片可預測性方面的可衡量成果 , 證明了 Cadence 如何實現大規模、可重復的 3D-IC 流片成功 。

利用3.5D集成技術擴展下一代AI ASIC在人工智能和機器學習 (ML) 加速器領域 , 大型語言模型 (LLM) 和深度學習推薦模型 (DLRM) 的快速發展對內存帶寬和計算密度提出了前所未有的要求 。 為了滿足這些需求 , 人工智能專用集成電路 (ASIC) 已從大型單芯片發展到由先進封裝技術支持的異構芯片架構 。

一家領先的基礎設施芯片供應商代表了一種日益增長的3D集成電路實現方案 , 通常被稱為“3.5D”集成 。 這種方法結合了大型光罩級邏輯芯片、2.5D中介層和選擇性3D芯片堆疊 , 以實現架構可擴展性 。 雖然這些設計功能強大 , 但在布局規劃、組裝正確性和芯片間連接方面卻帶來了重大挑戰 。

借助 CadenceIntegrity 3D-IC 平臺 , 設計團隊實施了一種“從設計之初就保證正確性”的布局規劃和組裝方法 , 從而在芯片和封裝結構中保持了系統意圖 。 該平臺無需依賴分散的工具交接 , 即可實現早期堆疊規劃、確定性連接定義以及貫穿整個構建過程的持續驗證 。

【突破先進工藝瓶頸:3D-IC成半導體創新核心引擎】最終實現了一次性成功制造ASIC芯片——這對于大規模AI加速器至關重要 , 因為重新設計芯片會帶來巨大的成本和進度風險 。 這個例子表明 , Cadence 3D-IC解決方案越來越注重可預測性和制造就緒性 , 而不僅僅是峰值性能 。

大規模芯片組設計的集成系統驗證云規模的工作負載對基于芯片組的系統架構提出了持續的壓力 , 要求在緊迫的部署期限內實現高性能 。 在一家大型云平臺提供商開發的先進多芯片計算平臺中 , 模塊化芯片組提高了可擴展性 , 但也增加了系統規劃、驗證和最終驗收的復雜性 。

傳統流程中最棘手的挑戰之一是 , 當扁平化的GDS數據傳輸到下游系統分析工具時 , 系統意圖容易丟失 。 多邊形抽象、轉換錯誤以及驗證步驟脫節常常導致錯誤的信號完整性(SI)和電源完整性(PI)違例 , 從而延長分析周期并減緩設計收斂過程 。

該方法顯著提高了芯片組裝過程中的生產效率 , 并縮短了整體分析時間 , 從而強化了 EDA 集成在實現成功且可擴展的異構集成方面的重要性 。

此次客戶部署展示了 Cadence 3D-IC 設計方法如何受益于緊密集成的規劃和分析 。 借助Integrity 3D-IC 平臺 , 在統一的在線設計環境中完成了多芯片構建、信號完整性 (SI) 和性能完整性 (PI) 分析 。 直接在構建過程中進行切割分析消除了轉換誤差 , 并使結果能夠直接反向標注到物理實現中 。

該方法顯著提高了芯片組裝過程中的生產效率 , 并縮短了整體分析時間 , 從而強化了 EDA 集成在可擴展異構集成工作流程中的重要性 。

適用于先進 3D-IC 架構的可擴展電源完整性隨著3D集成電路架構復雜性的不斷增加 , 電源分配網絡(PDN)已成為一項主要的設計風險 。 垂直堆疊、高密度微凸塊陣列和多芯片交互作用暴露了傳統2D電源完整性方法的局限性 , 尤其是在先進節點上 。

來自一家領先半導體制造商的先進封裝案例研究表明 , Cadence 如何通過可擴展的電源完整性分析 , 助力實現可量產的 3D-IC 解決方案 。 該設計團隊利用Voltus IC 電源完整性解決方案、 Innovus 實施系統和 Integrity 3D-IC 平臺 , 實施了一套全面的電源完整性 (PI) 方法 , 涵蓋從早期探索到最終驗收的整個過程 。

兩種技術被證明效果尤為顯著 。 自適應分區將具有相似空間特征的芯片分組 , 減少了不必要的仿真迭代次數 , 提高了收斂速度 。 而基于XM的分層建模實現了高精度的宏觀抽象 , 在保持簽核級精度的同時 , 顯著縮短了EM-IR仿真周期 。

在一個包含約 10 萬個凸點的先進 2.5D 設計中 , EM-IR 測試周期縮短了 10% 以上 , 而對精度的影響微乎其微 。 在規模更大的分層設計中 , 仿真時間縮短了 50% 以上 , 電源和接地節點數量也從數十億減少到可控水平 。 這些結果凸顯了 Cadence 3D-IC 設計成果越來越注重生產效率、可擴展性和可靠性 , 而不僅僅是性能 。

面向大批量生產的代工廠級3D-IC制造流程除了在各個客戶項目中取得的成功部署之外 , Cadence 的 3D-IC 生態系統實力還得益于與領先半導體代工廠的深度持續合作 。 通過與代工廠的緊密協作 , Cadence 提供經過生產驗證的 3D-IC 設計流程 , 這些流程經過認證、驗證 , 并針對制造就緒性進行了專門設計 , 而不僅僅是設計可行性 。

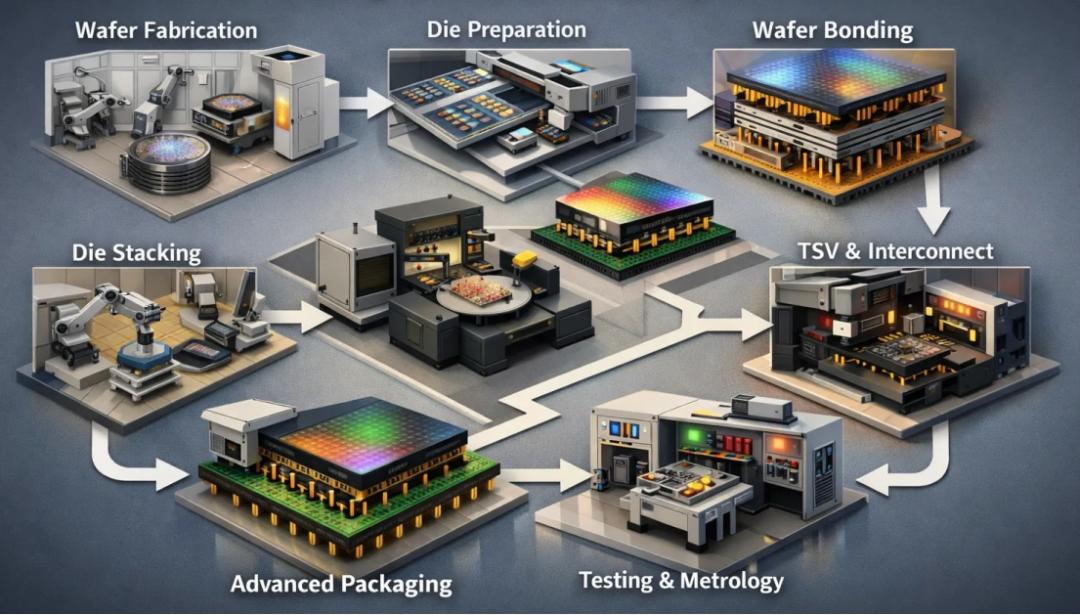

可擴展3D-IC制造工作流程的代表性可視化

Cadence 多芯片3D-IC 解決方案支持多種先進集成技術 , 包括復雜的芯片堆疊結構、混合鍵合、硅和有機中介層 , 以及新興的代工廠專用封裝創新技術 。 這些功能與Clarity 3D Solver、Sigrity X Platform、Celsius Thermal Solver和 Voltus IC 電源完整性解決方案緊密集成 , 從而在整個設計周期中實現系統級的SI、PI、熱分析和可靠性分析 。

通過將代工廠要求直接嵌入到 3D-IC 工作流程中 , 這種經過代工廠認證的方法使設計團隊能夠更有信心地從架構探索過渡到流片 , 從而降低晶圓堆疊、中介層實現和封裝感知簽核等環節在大批量生產環境中的風險 。

這些3D-IC成功案例揭示了什么?

在這些 Cadence 3D-IC 案例研究中 , 涌現出幾個共同的主題:

- 成功的3D-IC項目將封裝視為首要的設計對象 。

- 早期、綜合的多物理場分析對于減少重自旋至關重要 。

- 分層和分區方法對于可擴展性至關重要 。

- 制造意識必須融入生產環節 , 而不是事后添加 。

擴大可重復3D-IC流片成功率隨著異構集成成為下一代系統的基礎 , 設計成功不僅僅取決于創新的架構 , 還需要可重復、可量產且能夠跨產品、節點和市場擴展的工作流程 。

Cadence Integrity 3D-IC平臺結合系統、功耗、信號和熱分析功能 , 使團隊能夠自信地從概念階段過渡到芯片階段 。 這些Cadence 3D-IC的成功案例不僅展現了孤立的成果 , 更體現了一種可擴展的方法 , 能夠在先進封裝時代實現更快的帶寬、更低的功耗和可預測的流片結果 。

*聲明:本文系原作者創作 。 文章內容系其個人觀點 , 我方轉載僅為分享與討論 , 不代表我方贊成或認同 , 如有異議 , 請聯系后臺 。

想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- AMD顯卡明年史詩級升級:2nm工藝 AI性能提升1000倍

- Lightricks-2 AI視頻模型實現設備端運行突破

- 臺積電2nm制程工藝 預計會在三季度開始產生營收

- 英特爾推出首批18A工藝制程的Core Ultra處理器

- 中國芯片代工“三巨頭”崛起:全球前十占三席,28nm成突破關鍵

- 遙遙領先?iPhone17系列國內銷量突破1550萬臺

- 臺積電2nm工藝已如期量產 消息稱主生產基地是晶圓二十二廠

- 擺脫先進制程依賴,日廠另辟蹊徑

- 「2025機圈年度總結」形態革新到體驗突破,創新技術回歸用戶需求

- 驍龍8 Elite Gen6首發臺積電2nm工藝:蘋果A20最強勁敵來了