文章圖片

文章圖片

文章圖片

文章圖片

本文由半導體產業縱橫(ID:ICVIEWS)編譯自pcwatch

規模完全是另一個層次 。

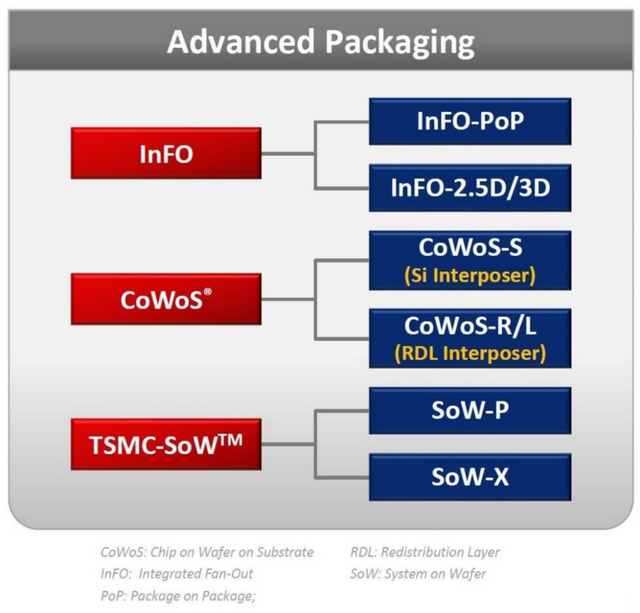

臺積電正積極研發先進封裝技術晶圓系統(SoW) , 將超大規模、超高速系統集成在直徑300毫米的大尺寸硅晶圓或相同直徑的圓盤狀載體(支撐體)上 。

SoW通過將多個硅片或微型模塊以二維矩陣排列 , 兼具超大規模、超高速的運算能力、高速、高密度的數據傳輸 , 以及降低功耗 。

InFO技術應用于低成本、高性能大封裝SoW技術的起源 , 在于臺積電針對移動處理器所研發的小型化、薄型化封裝技術InFO(Integrated Fan-Out) , 俗稱FO-WLP(Fan Out-Wafer Level Package) 。

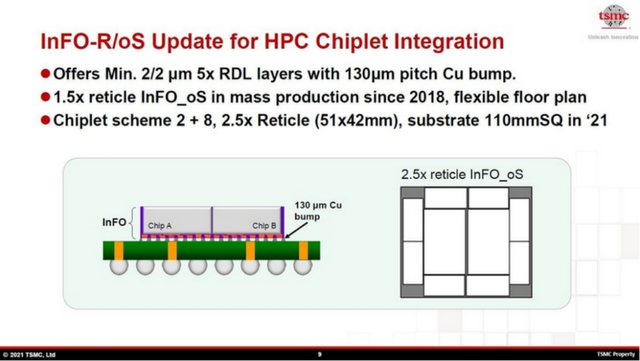

2020年前后 , 臺積電為高性能大規模邏輯(FPGA、GPU等)提供了CoWoS(晶圓上芯片)封裝技術 , 該技術利用硅中間基板(Si interposer)實現硅片(水平排列的芯片)之間的高密度連接 。 與此同時 , 臺積電還準備并量產了InFO_oS(晶圓上芯片)封裝技術 , 該技術利用InFO技術實現硅片之間的高密度連接 , 作為高性能大規模邏輯的低成本封裝 。

InFO_oS 的優勢在于尺寸擴展相對容易 , 并且通過為封裝基板選擇 InFO 的 RDL , 可以制作超多層布線板 。 2018 年開始量產尺寸為光罩尺寸 1.5 倍的 InFO_oS 。

InFO_SoW 是將 InFO_oS 的基板尺寸(RDL 尺寸)擴展至直徑 300 毫米的硅晶圓尺寸 。 InFO 的精細高密度再分布層 (RDL) 擴展至晶圓尺寸 , 并將眾多硅芯片面朝下(硅芯片的電路面朝向 RDL)放置在 RDL 上 。 將電源模塊和包含輸入/輸出 IC 的連接器安裝在放置硅芯片的 RDL 背面 , 即可形成系統模塊 。

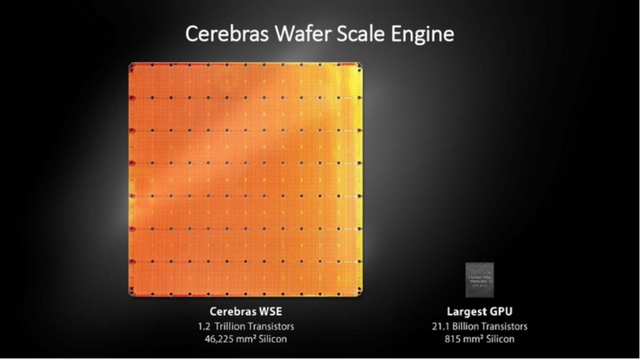

人工智能硬件開發商Cerebras Systems(以下簡稱 Cerebras)已將 InFO_SoW 技術應用于其深度學習加速器WSE(晶圓級引擎) 。 WSE 技術概述于 2019 年 8 月舉行的高性能處理器技術國際會議 Hot Chips 上發布 , 并在高性能處理器開發界引起了轟動 。 該公司還于 2019 年 8 月 19 日在新聞稿中正式宣布了 WSE 的開發 。

InFO_SoW 技術和 WSE 技術并不完全相同 。 最大的區別在于它們處理硅片的方式 。 InFO_SoW 技術假設芯片為小芯片 , 將許多使用不同制造技術制造的微型芯片(已確認良好的微型芯片)安裝在晶圓大小的 RDL 上 。 而 WSE 技術則在直徑為 300 毫米的硅晶圓上一次性制造 84 個微型芯片 。 這 84 個微型芯片通過劃線連接 , 整體形狀呈方形 。

在AI 處理器核心級對所有微型芯片進行測試后 , 會在微型芯片表面形成連接微型芯片之間以及處理器核心之間的布線(將成為 RDL 的一部分) 。 這種布線至關重要 。 測試中被判定為有缺陷的核心將被移除 , 并替換為冗余核心(在測試中被判定為良好) 。 換句話說 , 預計在測試后才能確定 RDL 中微型芯片表面側的布線布局 。

這只是猜測 , 但他們可能會制作一塊略大于微型芯片組的方形RDL 板 , 或者將預制的 RDL 板連接到微型芯片組上 。 RDL 板的尺寸為 215 毫米見方 , 其外接圓直徑為 304 毫米 , 略大于 300 毫米晶圓 。 Cerebras 發布的 WSE 照片包含 RDL 板 , 上面有許多通孔 。 這些通孔被認為是用來機械連接上下電源模塊、連接器和冷卻板的 。

InFO_SoW 在 WSE 的三代產品中繼續使用Cerebras 在 2019 年 8 月發布 WSE 之后 , 又于 2021 年 4 月發布了第二代晶圓級處理器 WSE-2 , 并于 2024 年 5 月發布了第三代晶圓級處理器 WSE-3 。 兩代產品均采用臺積電的 InFO_SoW 技術 , WSE 的尺寸(215 平方毫米)和芯片數量(84 個)保持不變 。

最大的區別在于硅芯片的制造技術 。 第一代采用16nm 工藝 , 對于 2019 年來說相當適中 。 2021 年發布的第二代 WSE-2 將微型化提升到了一個新的水平 , 并采用了 7nm 工藝 。 2024 年發布的第三代 WSE-3 選擇了 5nm 工藝 , 進一步實現了微型化 。 因此 , 第三代的晶體管數量增加到 4 萬億 , 是第一代 1.2 萬億的 3.3 倍多 。

Cerebras三代WSE都采用了300mm晶圓InFO_SoW技術 , 這體現出直徑大于300mm的晶圓并不存在 , 目前終極的大規模電路模塊是InFO_SoW技術 。

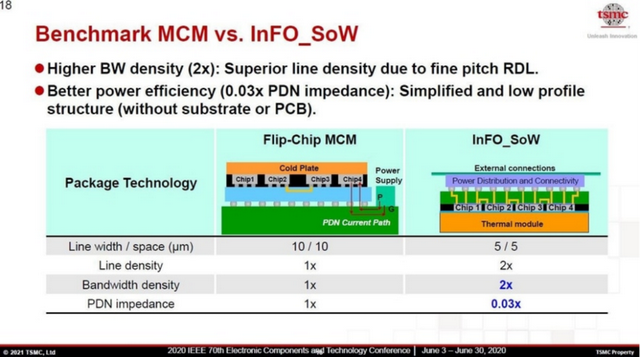

其基本性能是 , 與采用中間基板的多芯片模塊(MCM) 相比 , 硅片間的布線寬度/間距減少一半 , 布線密度增加一倍 , 單位長度的數據傳輸率增加一倍 。 最大的區別在于電源阻抗 , 僅為 MCM 的 1/33 。 這是因為 , 原則上 , 215 毫米見方的 RDL 層的整個背面都可以在電源模塊中布局 , 而且由于電源布線是垂直(縱向)的 , 因此布線長度極短 。 低電源阻抗對穩定電源電壓和降低功耗貢獻巨大 。

臺積電還在開發下一代InFO_SoW 技術 , 稱之為SoW-X (eXtreme) 。 臺積電最近還將之前開發的 InFO_SoW 技術更名為SoW-P 。

SoW-P 和 SoW-X 的區別在于 , 前者分布在同一處理器上 , 而后者分布在處理器(或 SoC)和內存模塊上 。

*聲明:本文系原作者創作 。 文章內容系其個人觀點 , 我方轉載僅為分享與討論 , 不代表我方贊成或認同 , 如有異議 , 請聯系后臺 。

【臺積電盯上的SoW封裝,到底是什么?】想要獲取半導體產業的前沿洞見、技術速遞、趨勢解析 , 關注我們!

推薦閱讀

- 遙遙落后的節奏!iPhone 17系列電池曝光,Air就是來搞笑的

- 首發8100毫安巨無霸電池!又一款性能續航王新機來了:價格很香!

- 二手筆記本電腦良莠不齊,惠普出手定標準了

- 今年5月中國大陸筆記本電腦線上市場銷量及銷額雙增長,均價直逼7000元

- 一加小屏手機也很香,16GB+512GB跌至3345元,驍龍8至尊版+大電池

- 媒體專訪Anker高管:問題電芯的款式可能生產了2000~3000萬片

- 步充電寶后塵 影視颶風補光燈也“火”了

- 學生黨預算不足想買二手電腦?全網最強避坑指南出爐:謹記三不買

- 別急!關于無3C認證的充電寶,市場監管總局正式回應

- 羅馬仕陷倒閉傳聞,充電寶行業能挺住嗎?