文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

文章圖片

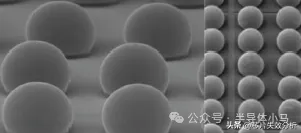

一、Bump介紹

在先進封裝中 , “Bump” 通常指凸塊 , 是一種關鍵的連接技術 。 它是在芯片表面制作的小凸起 , 一般只有幾十到幾百微米大小 , 主要作用是提供芯片與其他電子元件之間的電氣連接 , 從倒裝焊FlipChip出現就開始普遍應用了 , Bump的形狀也有多種 , 最常見的為球狀和柱狀 , 也有塊狀等其他形狀 。 Bump起著界面之間的電氣互聯和應力緩沖的作用 , 從Bondwire工藝發展FlipChip工藝的過程中 , Bump起到了至關重要的作用 。

隨著工藝技術發展 , Bump尺寸越來越?。 築ump的發展趨勢是尺寸不斷縮小 , 從球柵陣列焊球(BGA ball) , 其直徑范圍通常在0.25-0.76mm , 到倒裝凸點(FC Bump) , 也被稱為可控塌陷芯片焊點(C4 solder joint) , 其直徑范圍通常在100-150μm 。 行業內正朝著 20μm 甚至小于 10μm 的方向推進 , 凸點間距越小 , 凸點密度越高 , 封裝集成度越高 , 技術難度也越大 。 對于 20μm 以上的間距 , 可采用基于熱壓鍵合(TCB)的微凸塊連接技術 , 未來混合鍵合(HB)銅對銅連接技術有望實現 10μm 以下的凸塊間距和更高的凸點密度 , 并帶動帶寬和功耗雙提升 。

工藝流程:通常包括清洗、濺鍍、曝光、顯影、電鍍、去膠、蝕刻和良品測試等環節 。 具體而言 , 先在晶圓表面沉積鈦或鈦鎢作為阻擋層 , 再沉積銅等作為種子層;然后旋涂光刻膠 , 通過光刻曝光和顯影得到所需圖形;接著進行電鍍形成凸點下金屬化層(UBM) , 去除光刻膠并蝕刻掉多余的種子層和阻擋層;之后進行植球工序 , 將助焊劑和錫球印刷到 UBM 上;最后經過回流爐使錫球熔化與 UBM 形成良好結合 。

凸塊制造技術是諸多先進封裝技術實現和發展演化的基?。 壕嗄甑姆⒄?, 凸塊制作的材質主要有金、銅、銅鎳金、錫等 , 不同金屬材質適用于不同芯片的封裝 , 且不同凸塊的特點、涉及的核心技術、上下游應用等方面差異較大 。

一、金凸塊

主要特點:

優點:高導電性、抗腐蝕性強、鍵合工藝成熟、無需底部填充(Underfill) 。

缺點:成本高(黃金價格昂貴)、硬度低易變形、高溫下可能與焊料形成脆性金屬間化合物(IMC) 。

關鍵參數:典型尺寸為 50-150μm , 間距 100-250μm 。

應用領域:1)高頻、高可靠性器件:RF模塊、光通信器件、毫米波雷達;2)醫療、航空航天:植入式醫療設備、衛星電子元件;3)Flip Chip 封裝早期應用:如早期手機芯片、FPGA 。

工藝流程:

二、銅鎳金凸塊

主要特點:

優點:結合銅的低成本和金的抗腐蝕性 , Ni 層作為擴散阻擋層抑制 Cu-Sn IMC 生長 。

缺點:工藝復雜度高(三層金屬沉積) , 需嚴格控制 Ni 層厚度(過薄易穿透 , 過厚易脆) 。

關鍵參數:Cu柱高度50-100μm , Ni層厚度3-5μm , Au層厚0.3-1μm 。

應用領域:1)汽車電子:ECU(電子控制單元)、功率模塊;2)工業設備:高可靠性傳感器、控制器;3)消費電子:中高端手機攝像頭模組、指紋識別芯片 。

工藝流程:

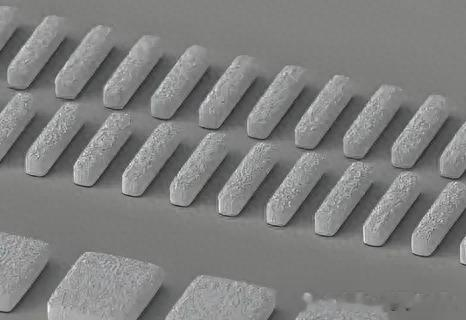

三、銅柱凸塊

主要特點:

優點:低電阻(銅導電性優于錫)、高熱導率、更好的機械穩定性(抗跌落測試)、適合細間距(≤50μm) 。

缺點:易氧化(需表面處理)、Cu-Sn IMC 生長可能導致可靠性問題 。

關鍵參數:Cu柱直徑 10-50μm , 高度 30-60μm , 表面通常有 Ni/Au 或 Sn/Ag 涂層 。

應用領域:1)高性能計算:CPU、GPU、HBM(高帶寬內存);2)5G 通信:RF 前端模塊、高速 SerDes 芯片;3)AI 芯片:需要高密度 I/O 的 ASIC、FPGA 。

工藝流程:

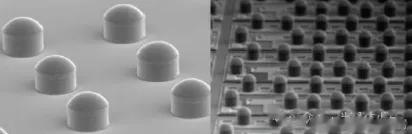

四、錫凸塊

主要特點:

【先進封裝四要素介紹】優點:工藝簡單、成本低、自對準能力強(回流時液態表面張力) 。

缺點:電性能較差(電阻高于銅)、熱循環可靠性有限(錫易疲勞) 。

關鍵參數:典型成分為 SnAgCu(SAC)合金 , 尺寸 30-200μm , 間距 50-400μm 。

應用領域:1)消費電子:智能手機、平板電腦、可穿戴設備;2)存儲芯片:DDR、NAND Flash 封裝;3)低成本/中低端器件:如 WiFi 模塊、藍牙芯片 。

工藝流程:

五、技術對比與選擇標準

凸塊類型

成本

電性能

熱性能

可靠性

工藝復雜度

最小間距

典型應用

金凸塊

高

優

良

優

低

100μm+

RF 器件

醫療設備

銅鎳金凸塊

中

良

良

優

中高

80μm+

汽車電子

工業控制

銅柱凸塊

中

優

優

良

高

≤50μm

HPC

5G

AI 芯片

錫凸塊

低

良

中

中

低

50μm+

消費電子

存儲芯片

六、Bump在Flip Chip(倒片封裝)中的應用

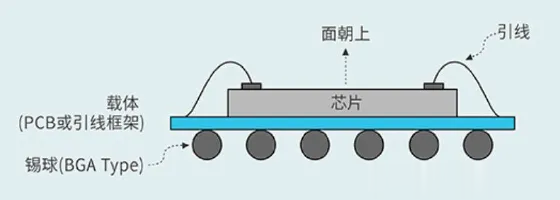

倒片封裝技術因其將芯片上的凸點翻轉并安裝于基板等封裝體上而得名 , 是一種實現芯片與板(如基板)電氣連接的互連技術 , 鍵合至基板或形成焊接凸點過程中不存在任何工藝方面限制;倒片封裝憑借其優越的電氣性能(不存在電氣連接I/O引腳數量和位置限制 , 電信號傳輸路徑短于引線鍵合) , 已經很大程度上取代了引線鍵合 。 倒片封裝體中凸點(Bump)是基于晶圓級工藝而完成的 , 而后續工序則與傳統封裝工藝相同 。

引線鍵合示意圖

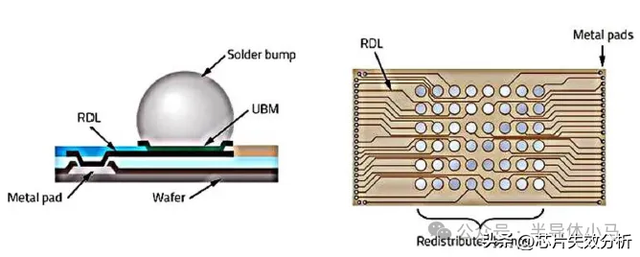

倒裝芯片綁定示意圖

倒裝芯片凸點制作工藝流程

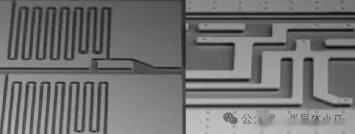

二、RDL介紹

RDL(Redistribution Layer)即重分布層 , 是先進封裝中實現芯片水平方向電氣延伸和互連的關鍵技術 , 在 3D/2.5D 封裝集成以及 FOWLP(扇出型晶圓級封裝)中應用廣泛 。

一、工作原理

通過在芯片表面沉積金屬層和相應的介電層 , 形成金屬導線 , 將 IO 端口重新設計到更寬敞的區域 , 構建出表面陣列布局 。 簡單來說 , 就是把芯片原本位于邊緣或四周的 I/O 觸點 , 通過半導體工藝延伸到芯片表面其他位置 , 擴展布局到占位更寬松的區域 , 實現 I/O 觸點的重新布線 。

二、優勢

降低設備成本:打破了傳統封裝中昂貴且耗時的引線鍵合和倒裝芯片鍵合工藝的束縛 , 通過減少設備所需的元件數量 , 有效降低設備成本 。

減少占地面積:可將多個芯片集成到單個封裝中 , 極大地減少器件的整體占地面積 , 滿足智能手機、可穿戴設備等對空間要求極高的產品需求 。

改善電氣性能:RDL 中介層信號通孔尺寸極小 , 可大幅改善 SerDes 信號完整性 , 其金屬厚度優勢也能提升內存 SI , 同時低損耗介電材料可降低介電損耗 , 優化整個封裝的電氣性能 。

提高設計靈活性:RDL介質層利用精細的線路寬度和間距 , 減少路由干擾 , 支持更多引腳數量 , 使 I/O 觸點間距更靈活 , 凸點面積更大 , 為芯片設計提供更大自由度 。

三、工藝流程

在重新分配層工藝中 , 首先通過濺射工藝創建一層金屬薄膜 , 之后在金屬薄膜上涂覆厚層光刻膠 。 隨后利用光刻工藝繪制電路圖案 , 在電路圖案的曝光區域電鍍金層 , 以形成金屬引線 。 由于重新分配工藝本身就是重建焊盤的工藝 , 因此確保引線鍵合強度是十分重要的 。 這也正是被廣泛用于引線鍵合的材料—金 , 被用于電鍍的原因 。

四、應用領域

RDL 技術已廣泛應用于MEMS器件、傳感器、功率器件、存儲器、微處理器和圖形處理器等眾多領域的封裝 , 為實現更小、更快、更高效的芯片設計提供技術支撐 。

在WLP中:在FIWLP/FOWLP中 , RDL是最為關鍵的技術 , 通過RDL將IOPad進行扇入Fan-In或扇出Fan-Out , 形成不同類型的晶圓級封裝 。

在2.5D中:除了硅基板上的TSV , RDL同樣不可或缺 , 通過RDL將網絡互聯并分布到不同的位置 , 從而將硅基板上方芯片的Bump和基板下方的Bump連接 。

在3D中:對于上下堆疊是同一種芯片 , 通常TSV就可以直接完成電氣互聯功能了 , 而堆疊上下如果是不同類型芯片 , 則需要通過RDL重新布線層將上下層芯片的IO進行對準 , 從而完成電氣互聯 。

五、技術發展

目前 4 層 RDL 技術已經成熟 , 良率可達 99% , 能滿足約 85% 的封裝需求 。 未來 , RDL 工藝將朝著提高粘附力 , 減少熱循環過程中的機械應力和熱應力的方向發展 , 同時對布線檢測等設備也提出了更高要求 。

三、Wafer

在先進封裝四要素中 , Wafer(晶圓)是集成電路的基礎載體 , 也是RDL 和TSV的介質和載體 。

一、材料與結構

晶圓通常是薄片狀的硅片 , 現代晶圓幾乎是純硅材料 , 雜質含量極低 , 晶體結構需非常完美 , 以避免制造過程中產生缺陷 。 此外 , 還有化合物半導體材料晶圓 , 如氮化鎵(GaN)和碳化硅(SiC)晶圓 , 適用于 5G 通信、射頻器件和電動汽車等高端應用場景 。

二、尺寸規格

其尺寸(直徑)隨著工藝進步不斷擴大 , 早期晶圓直徑只有幾英寸 , 現代已達到300mm(12 英寸) , 甚至正在開發450mm(18 英寸)的晶圓 。 更大的晶圓尺寸意味著一片晶圓上可加工的芯片數量增加 , 能提高生產效率并降低成本 。

三、作用與功能

晶圓是制造集成電路(IC)的平臺 , 所有的芯片電路都在晶圓上進行加工形成 , 每一個芯片(Die)都是從晶圓上切割下來的 。 同時 , 可以在Wafer上制作硅基板實現2.5D集成 , 也是 WLP(晶圓級封裝)的承載晶圓 。

四、工藝要求

為滿足芯片尺寸不斷縮小和集成度不斷提高的需求 , 對晶圓純度、平整度和結構缺陷控制要求極高 。 晶圓制造需在高度控制的環境下進行 , 包括生長單晶硅棒、切割、拋光和清洗等一系列復雜工藝 。

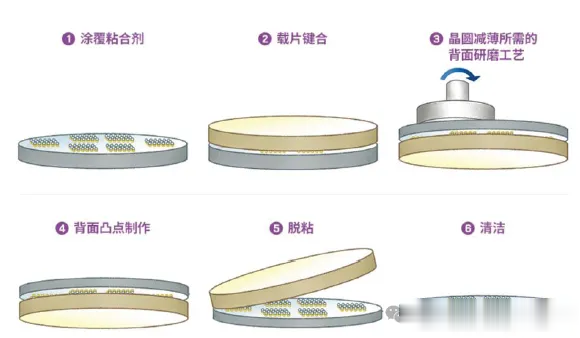

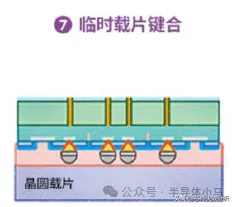

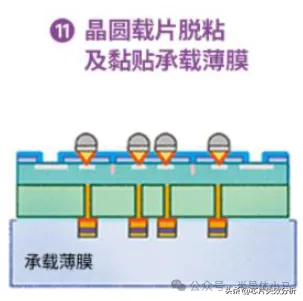

晶圓承載系統工藝:是指針對晶圓背面減薄進行進一步加工的系統 , 該工藝一般在背面研磨前使用 。 晶圓承載系統工序涉及兩個步驟:首先是載片鍵合 , 需將被用于硅通孔封裝的晶圓貼附于載片上;其次是載片脫粘 , 即在如晶圓背面凸點制作等流程完工后 , 將載片分離 。

晶圓邊緣切筋工藝:對于采用硅通孔工藝封裝的晶圓 , 在其進行載片鍵合前 , 應先對晶圓正面邊緣進行切筋并去除修剪部分 。

五、發展趨勢

隨著先進封裝技術向更小的節點(如3nm、2nm)發展 , 晶圓制造工藝也在不斷進步 , 將更依賴于不同類型晶圓(如硅基和化合物半導體基晶圓)的結合 , 以實現高效能的芯片封裝和集成 。

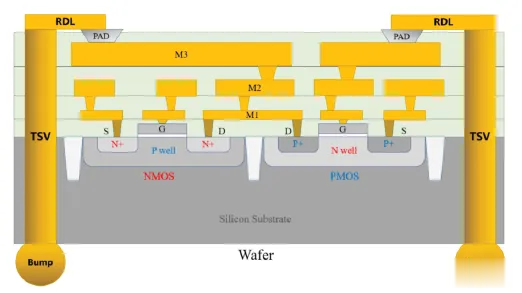

四、TVS介紹

TSV(Through - Silicon Via , 硅通孔)是先進封裝技術中的一種關鍵垂直互連技術 。 它通過在芯片內部打通通道 , 實現電氣信號的垂直傳輸 , 可顯著提高芯片之間的數據傳輸效率 , 減少信號延遲 , 降低功耗 , 并提升封裝的集成密度 。

一、工作原理

基于硅片中的深孔刻蝕技術 , 先在硅片中打孔 , 再填充銅等導電材料形成電氣連接 。 這些通孔貫穿整個芯片厚度 , 可將不同芯片層或同一芯片內的不同電路相互連接 , 作為芯片與芯片、芯片與封裝基板、以及芯片內部不同電路層之間的高效電氣通道 。

二、分類

2.5D封裝中的TSV:通常用于中介層(Interposer) 。 中介層是帶有 TSV 的載體 , 可承載多個芯片 , 如處理器和內存等 , 芯片通過 TSV 在中介層上互連 , 而非直接堆疊 , 主要應用于高性能計算和數據中心芯片等需要高度互連和高帶寬的系統 。

3D 封裝中的 TSV:實現了芯片的垂直堆疊 , 每個芯片層通過 TSV 直接相互連接 , 形成一個整體 , 能讓不同功能模塊 , 如處理器和內存高度集成在同一個封裝中 , 提高芯片集成密度和性能 , 同時減小封裝尺寸 。

Via-last TSV:TSV制作可以集成到生產工藝的不同階段 , 通常放在晶圓制造階段為Via-first , 封裝階段為Via-last(該方案可以不改變現有集成電路流程和設計 , 目前業界已開始在高端的Flash和DRAM領域采用Via-last技術 , 即在芯片周末進行硅通孔的TSV制作 , 然后進行芯片或晶圓層疊 。

Via-middle(中通孔)封裝工藝:首先在晶圓制造過程中形成通孔 , 隨后在封裝過程中 , 于晶圓正面形成焊接凸點 。 之后將晶圓貼附在晶圓載片上并進行背面研磨 , 在晶圓背面形成凸點后 , 將晶圓切割成獨立芯片單元 , 并進行堆疊 。

三、工藝流程

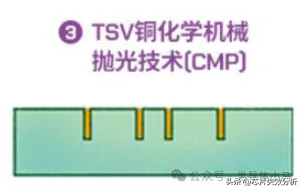

中通孔基本工序:首先在晶圓上制作晶體管 , 隨后使用硬掩模在硅通孔形成區域繪制電路圖案 , 之后利用干刻蝕工藝去除未覆蓋硬掩膜的區域 , 形成深槽;再利用CVD工藝制備絕緣膜(用于隔絕填入槽中的銅等金屬物質 , 防止硅片被金屬物質污染);此外絕緣層上還將制備一層金屬薄層(將被用于電鍍銅層)作為屏障;電鍍完成后 , 采用CMP技術使晶圓表面保持平滑 , 同時清除其表面銅基材 , 確保銅基材只留在溝槽中 。

來源:半導體封裝工程師之家

推薦閱讀

- 半導體封裝生產線工藝流程研究

- 揭秘 IGBT 模塊封裝與流程

- 芯片封裝失效典型現象

- 北方華創發布12英寸先進低壓化學氣相硅沉積立式爐設備

- 臺積電盯上的SoW封裝,到底是什么?

- 被低估的芯片封裝:院士稱我們落后國際,可能2-6年

- 比蘋果先進2年!華為最激進的手機曝光:外觀性能太猛了

- 新EDA工具推出,用于小芯片集成、封裝驗證

- 華為申請“四芯片”封裝專利 布局下一代AI芯片昇騰910D

- 蘋果在嘗試利用生成式人工智能設計芯片 高管稱設計芯片需要先進工具