【為先進制程工藝演進筑基!英特爾代工多領域相關技術突破淺析】

文章圖片

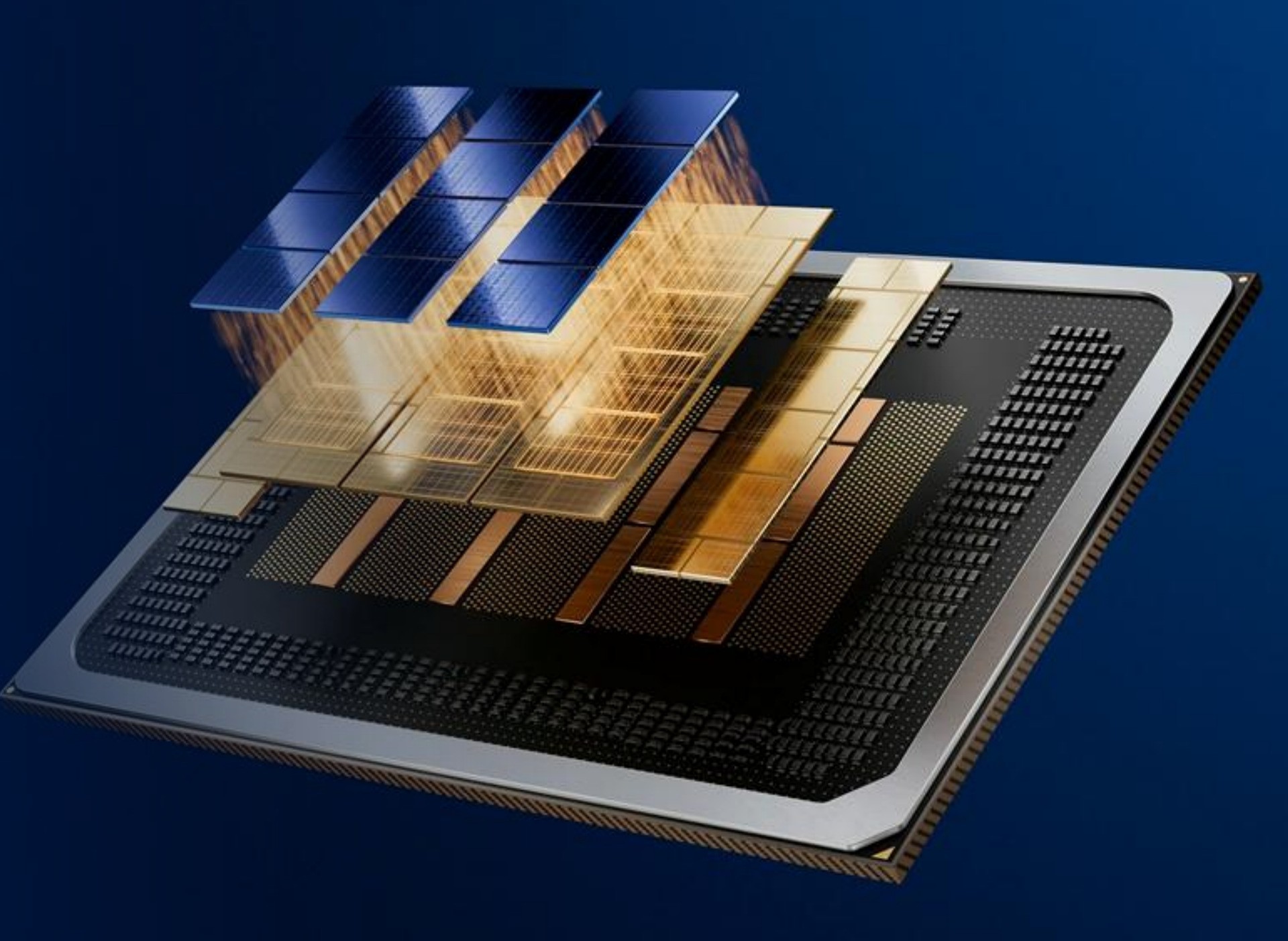

了解半導體技術的朋友都知道 , 當晶體管微縮到納米級之后 , 供電穩定性就一直是關系芯片性能和可靠性的關鍵因素 。 當下 , 英特爾即將通過Intel 18A制程工藝將先進制程從納米時代推向埃米時代 , 晶體管尺寸的進一步微縮雖然可以降低電壓 , 但是對于瞬時電流的需求也將不斷增加 , 因此非常容易導致電壓波動引發的計算錯誤甚至系統崩潰 。 同時 , 晶體管尺寸越小 , 對于“電源噪聲”愈加敏感 , 微小的電壓波動都會更加顯著地影響其開關速度和功耗 , 從而誘發穩定性問題 。

而為了解決這一問題 , 英特爾代工的研究人員展示了三種前景光明的MIM堆疊材料 , 包括:鐵電鉿鋯氧化物(HZO)、氧化鈦(TiO)以及鈦酸鍶(STO) 。 這些材料可以被應用于去耦電容 , 并且與標準芯片后端制造工藝兼容 。 其每平方微米60至98fF/μm2(飛法拉)的平面電容值 , 在不犧牲可靠性指標(如漏電、電容漂移、擊穿電壓)的前提下 , 相比當前先進技術實現了電容值的大幅提升 。 并且尤為重要的是 , 這些MIM堆疊材料在可靠性方面更加出色 , 漏電水平比業界目標低1000倍 , 能夠高效濾除電源噪聲 , 確保供電純凈 , 而且與現有后端制造工藝兼容就意味著可以直接應用于先進制程 。 這些方案研究證明了在下一代先進CMOS工藝中 , 一系列穩定、低漏電的MIM電容密度增強技術具有相當的應用潛力 。

此外 , 英特爾代工還在超薄GaN芯粒技術、靜默數據錯誤、微縮二維場效應晶體管(2D FETs)的可靠性、二維場效應晶體管中的選擇性邊緣工藝以及CMOS微縮等半導體先進制程領域的相關前沿技術層面取得了進展 。

在超薄GaN芯粒技術方面 , 英特爾的研究人員展示了業界領先的基于300毫米硅晶圓打造的功能完整的氮化鎵(GaN)芯粒 , 它主要面向高性能、高密度、高效率的電力電子以及高速射頻電子(RF Electronics)應用 。 這項技術突破實現了僅19微米(?m)的超薄芯粒 , 它比一根人類頭發還要薄 。 同時還配有完整的集成數字控制電路庫 , 有望解決下一代高性能電力和射頻(RF)電子器件在供電與效率方面的挑戰 。

同時 , 這項技術具備業界領先的功能完備、片上集成的CMOS數字電路庫:從邏輯門、多路復用器、觸發器到環形振蕩器 , 全部基于單片集成的氮化鎵N型金屬氧化物半導體高電子遷移率晶體管(GaN N-MOSHEMT)與硅基 P溝道金屬氧化物半導體場效應晶體管(Si PMOS) 工藝實現 。

而且在可靠性測試上的表現也極為優異——在時間依賴介質擊穿(TDDB)、正偏置溫度不穩定性(pBTI)、高溫反向偏壓(HTRB)以及熱載流子注入(HCI)等測試中取得了不錯的結果 , 表明該300毫米GaN MOSHEMT技術能夠滿足所需的可靠性指標 。

在靜默數據錯誤方面 , 英特爾的研究人員展示了傳統制造測試會如何遺漏一些關鍵缺陷 , 而這些缺陷會導致數據中心處理器出現靜默數據損壞 , 因此需要采用多樣化的功能測試方法來確保大規模部署的可靠性 。

此前 , 多項行業研究表明 , 由制造缺陷引起的靜默數據錯誤(SDE)或其它形式的靜默數據損壞(SDC) , 可能會在大規模部署于數據中心的系統級芯片(SoC)設備中發生 。 雖然結構化測試技術(如掃描測試)是制造測試的重要組成部分 , 但為了滿足云數據中心對質量的要求 , 還必須執行基于系統的功能測試 。 本研究分享了從多代的服務器SoC中獲得的結果 , 這些結果說明了使用大量多樣化功能測試的重要性 , 例如英特爾Data Center Diagnostic Tool測試套件中所包含的功能測試 , 用于篩查那些在運行中表現為靜默數據錯誤的缺陷 。

在微縮二維場效應晶體管(2D FETs)的可靠性層面 , 英特爾與維也納工業大學的研究人員全面測試了兩種晶體管技術的穩定性與可靠性:平面和GAA場效應晶體管 。 這兩種器件都采用單層(1-L)二硫化鉬(MoS?)溝道 , 并使用非晶態氧化鉿(HfO?)柵極堆疊結構:平面結構的HfO?厚度為4.3 nm , GAA結構為4.5 nm 。 然而 , GAA是微縮的二維場效應晶體管 , 具有納米級尺寸 , 可觀測到單個原子電荷俘獲事件 。

事實上 , 二維溝道在接近微縮極限的互補場效應晶體管(CFET)結構中 , 可能在性能上超越硅 。 然而 , 在層狀范德華(vdW)溝道與柵氧化層之間形成高質量界面 , 仍然是二維場效應晶體管的一大挑戰 。

在該項研究中 , 其主要目標是在滯回效應(hysteresis)、偏壓溫度不穩定性(BTI)以及隨機電報噪聲(RTN)測試方面對這兩種技術進行比較 。 這些測試結果將有助于更好地理解氧化層內部以及溝道/絕緣體界面處的陷阱物理機制(trap physics) 。

在用于可與晶圓廠工藝兼容的頂接觸、替換氧化層以及二維場效應晶體管層間去除的選擇性刻蝕工藝方面 , 過渡金屬二硫族化物(TMDs)有兩個較少被利用的特性 , 其一是在某些濕法刻蝕劑中表現出的極高化學穩定性 , 其二是其獨特的各向異性范德華結構 。 基于此 , 英特爾和IMEC的研究人員利用這兩個特性 , 實現了對氧化物帽層的選擇性凹陷刻蝕 , 并在300毫米試生產線中制造了具有類鑲嵌(damascene)型頂接觸的二維場效應晶體管 , 器件包括單層二硫化鎢(WS?)、單層二硫化鉬(MoS?)以及多層二硒化鎢(WSe?) 。

此外 , 這項技術還擴展應用于替換氧化物堆疊結構 , 并通過液體插層方法實現了層間的選擇性去除 , 將頂柵的電容等效厚度從2.5nm降低到1.5nm 。 這些成果構成了二維集成的三個全新的基礎技術模塊 。

英特爾與IMEC的合作 , 改進了用于源極和漏極接觸形成和柵極堆疊集成的技術模塊 , 可與晶圓廠更好地實現兼容(fab-comatible) , 同時降低了等效氧化層厚度(EOT) 。

(10967510)

推薦閱讀

- 賽力斯高管喊話華為,合作不能斷,用戶早把車當“華為牌”了

- 賽力斯正式回應“早日脫離華為”后,一個奇怪的現象出現了

- 都是做副屏的,為啥小米17Pro賣爆了,其他都涼了?

- 訂單多到“吞不下”:臺積電CoWoS先進封裝全線滿載,啟動外包保障交付

- 華為終于妥協,從4199元跌至2749元,IP69+衛星通話+100倍變焦

- 豆包踢開Agent大門,但微信說不定先進門

- 被OpenAI開除的年輕人投資了一家為OpenAI對手提供算力的初創

- 官宣,QQ 經典版回歸!

- 華為這個新產品,活成了微軟自己想象中的樣子

- 華為重磅亮相2025數智科技生態大會,以創新引領數智生活發展